$N^{\circ}$  d'ordre : 216

# École Doctorale Mathématiques, Sciences de l'Information et de l'Ingénieur UdS – INSA – ENGEES

# THÈSE

présentée pour obtenir le grade de

# Docteur de l'Université de Strasbourg Discipline : Sciences pour l'Ingénieur (spécialité Génie des Procédés)

par

# Özge TÜZÜN

# Polycrystalline Silicon Films by Aluminium Induced Crystallization and Epitaxy: Synthesis, Characterizations and Solar Cells

Soutenue publiquement le 28 septembre 2009

## Membres du jury

Directeur de thèse: M. Abdelilah Slaoui, Directeur de Rech., CNRSRapporteur externe: Mme. Anne Kaminski-Cachopo, Maître de Conf., INSA LyonRapporteur externe: M. Pere Roca i Cabarrocas, Directeur de Rech., CNRSExaminateur: M. Aziz Dinia, Professeur, Université de StrasbourgExaminateur: M. Alain Straboni, Professeur, Université de PoitiersExaminateur: M. Ivan Gordon, Ingénieur de Rech., IMEC, Leuven (B)

# **DEDICATION**

To my parents, Özcan and Şener Tüzün, for their support and patience.

#### ACKNOWLEDGEMENTS

I would like to express my deepest appreciation to my supervisor, Dr. Abdelilah Slaoui, for encouraging me to start my Ph.D. in InESS; furthermore for his advice, expertise, encouragement and proof-reading of this thesis, as well as for always making himself available for discussions and guidance whenever it was needing throughout the whole thesis. It was an absolute pleasure for me to have worked with such high quality and motivating scientists with immense scientific experience, knowledge, perceptiveness.

My special thanks go to my former supervisor Prof. Şener Oktik, who firstly taught me the skills of solar cells, for accepting me as a research student in Muğla University; for being guide and supportive.

I would like to extend my sincere appreciation to Prof. Daniel Mathiot for giving me the opportunity to carry out my research in InESS.

I wish to thank to Dr. Anne Kaminski-Cachopo, Dr. Pere Roca i Cabarrocas, Prof. Aziz Dinia, Prof. Alain Straboni, Dr. Ivan Gordon to be members of my dissertation committee.

Most and for all I thank Dr. Ivan Gordon for supervising my work; for being supportive and giving me all opportunities for my experiments; for all I was able to learn the details of AIC.

The work presented here would not have been possible without the support of Prof. Mehmet Güneş and Dr. Görkem Oylumluoğlu. I am especially thankful to them.

Many thanks go to Alexandru Focsa, Stephane Roques, Sébastien Schmitt, Marianne Amann and Nicolas Zimmermann for sharing their helpful advices on experiments and laboratory training; for helpful instructions on physics, processing and characterization.

I am happy to express my many thanks to my colleagues Marzia Carrada, Gérald Ferblantier, Prathap Pathi, Bhabani Sahu and my room mate Florian Delachat for their nice company, for their helps, kindness, friendship and hospitality during my PhD.

I want to thank Dr. Claire Maurice for EBSD measurements, Dr. Dominique Ballutaud for SIMS measurements, Dr. Paul Montgomery for interference microscopy measurements, Sophie Vallon for providing CORNING glass-ceramic substrates, Yu Qiu for the helps regarding solar cell fabrication, and Srisaran Venkatachalam in respect to epitaxy process.

Most importantly, I wish to thank my parents and all my friends for their helpfulness and constant moral support, leading my work successful.

I would like to acknowledge the financial support by Muğla University, Turkey.

| Ded      | Dedication                                                                 |     |  |  |  |

|----------|----------------------------------------------------------------------------|-----|--|--|--|

| Ack      | owledgements                                                               | iii |  |  |  |

| Con      | ents                                                                       | v   |  |  |  |

| Abstract |                                                                            |     |  |  |  |

| СН       | PTER 1: INTRODUCTION                                                       | 1   |  |  |  |

| 1.1      | Photovoltaic Energy Source                                                 | 1   |  |  |  |

| 1.2      | Photovoltaic Materials & Technologies                                      | 3   |  |  |  |

|          | 1.2.1 Bulk Silicon Solar Cells                                             |     |  |  |  |

|          | 1.2.2 Thin Film Compound and Organic Solar Cells                           | 5   |  |  |  |

|          | 1.2.3 Thin Film Silicon Solar Cells                                        | 9   |  |  |  |

|          | i) Amorphous silicon (a-Si) solar cells                                    |     |  |  |  |

|          | ii) Micromorph (a-Si/µc-Si) silicon solar cells                            |     |  |  |  |

|          | iii) Polycrystalline (poly-Si) silicon solar cells                         |     |  |  |  |

| 1.3      | Objective and Outline of the Thesis                                        | 16  |  |  |  |

| REF      | RENCES                                                                     | 17  |  |  |  |

| СН       | PTER 2: POLYCRYSTALLINE SILICON THIN FILMS                                 | 19  |  |  |  |

| 2.1      | Properties of Poly-Si                                                      | 19  |  |  |  |

|          | 2.1.1 Crystallographic Properties of Polycrystalline Materials             | 19  |  |  |  |

|          | 2.1.2 Impurities in Polycrystalline Materials                              | 24  |  |  |  |

|          | 2.1.3 Electrical Properties                                                |     |  |  |  |

|          | i) Majority carrier transport                                              |     |  |  |  |

|          | ii) Minority carrier transport                                             |     |  |  |  |

|          | iii) Comparison of electrical properties of N-type and P-type Si materials |     |  |  |  |

| 2.2      | 2 Polycrystalline Silicon Layer Formation Methods                          |     |  |  |  |

|          | 2.2.1 Direct Deposition Approach                                           |     |  |  |  |

|          | i) Chemical vapor deposition (CVD) at high temperature (≥1000°C)           |     |  |  |  |

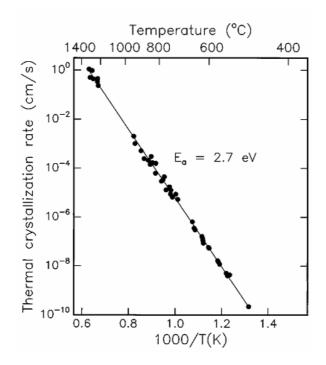

|          | ii) Solid phase crystallization (SPC)                                      |     |  |  |  |

# CONTENTS

|     | 2.2.2                                                         | Seed Layer Approach                                                       | 42   |  |  |

|-----|---------------------------------------------------------------|---------------------------------------------------------------------------|------|--|--|

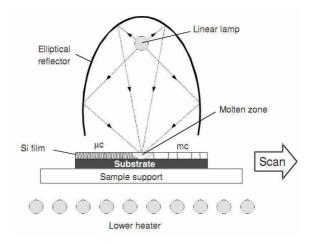

|     | i)                                                            | Zone melting crystallization (ZMC)                                        | 42   |  |  |

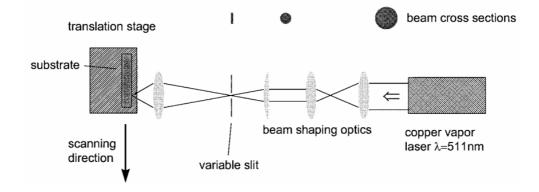

|     | ii) Laser induced crystallization (LIC)                       |                                                                           |      |  |  |

|     | iii                                                           | i) Metal induced crystallization (MIC)                                    | 47   |  |  |

| REF | FEREN                                                         | CES                                                                       | 49   |  |  |

| СН  | APTE                                                          | R 3: ALUMINIUM INDUCED CRYSTALLIZATION                                    | 53   |  |  |

| 3.1 | Princ                                                         | iple of Aluminium Induced Crystallization                                 | 53   |  |  |

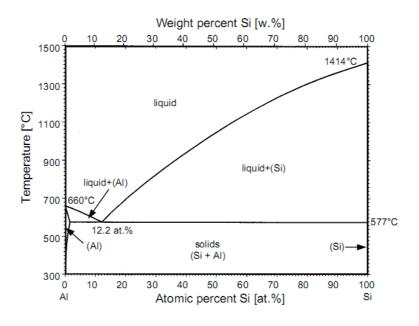

|     | 3.1.1                                                         | Solid Solubility of Al-Si System                                          | 53   |  |  |

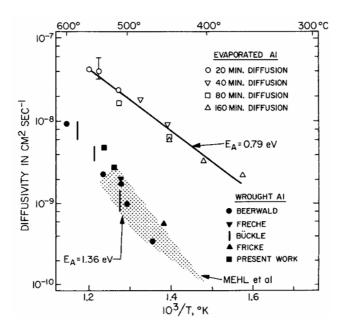

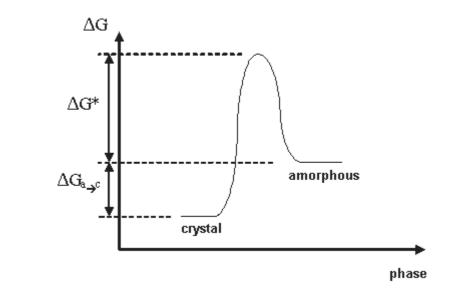

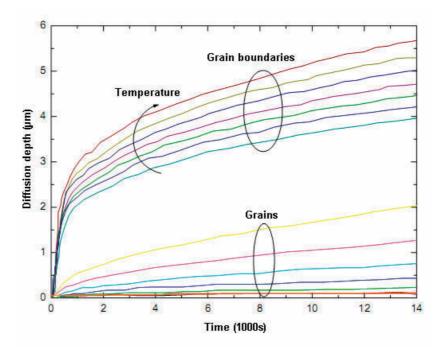

|     | 3.1.2                                                         | Diffusion of Silicon in Aluminium                                         | 54   |  |  |

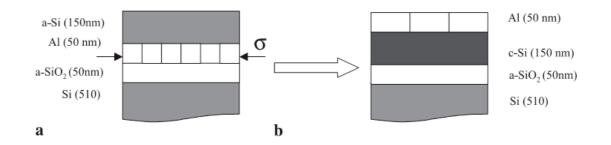

|     | 3.1.3                                                         | Thermodynamics and Kinetics of Al/Si Bilayers                             | 55   |  |  |

| 3.2 | State                                                         | of the Art of AIC Process                                                 | 61   |  |  |

| 3.3 | Analysis of Poly-Si Films Formed on Alumina and Glass-Ceramic |                                                                           |      |  |  |

|     | 3.3.1                                                         | Experimental Process for Formation of AIC Layers                          | 64   |  |  |

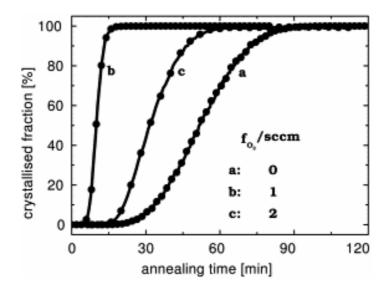

|     | 3.3.2                                                         | Effect of the Interfacial Oxide Layer (AlO <sub>x</sub> )                 | 67   |  |  |

|     | 3.3.3                                                         | Effect of the Aluminium Layer                                             | 70   |  |  |

|     | 3.3.4                                                         | Effect of Substrate                                                       | 77   |  |  |

|     | i)                                                            | Potential substrates                                                      | 77   |  |  |

|     | ii)                                                           | ) Properties of used substrates and their coating                         | 79   |  |  |

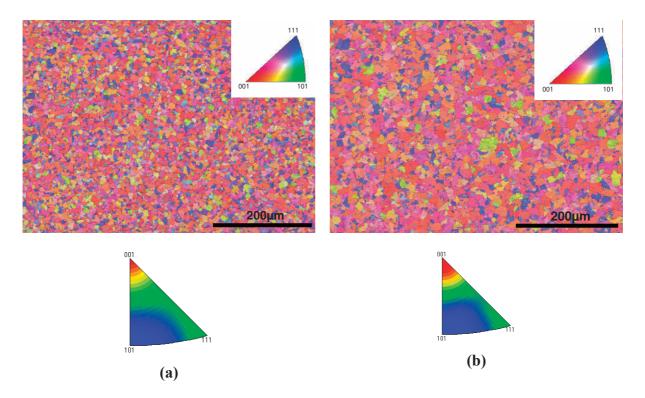

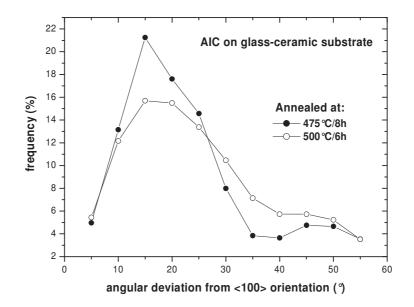

|     | iii                                                           | i) Effect of substrate on the crystallographic quality                    | 85   |  |  |

|     | 3.3.5                                                         | Effect of the Thermal Budget (Temperature and Time)                       | 91   |  |  |

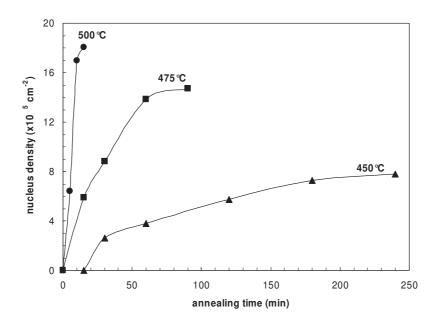

|     | i)                                                            | Nucleation kinetics during AIC                                            | 91   |  |  |

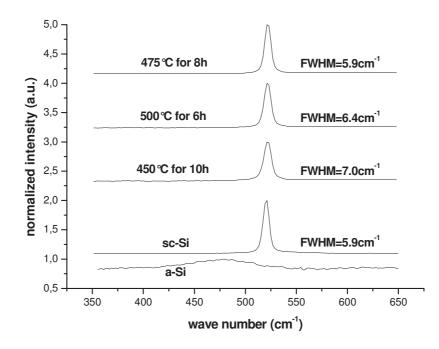

|     | ii)                                                           | ) Structural properties of continuous polysilicon films on glass ceramics | 95   |  |  |

|     | 3.3.6                                                         | Electrical Properties of the AIC Polysilicon Layer on Glass Ceramics      | s100 |  |  |

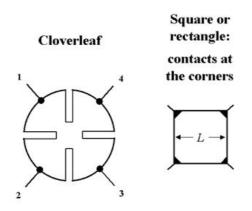

|     | i)                                                            | Hall effect system                                                        | 100  |  |  |

|     | ii)                                                           | ) Hall measurement on AIC approach                                        | 101  |  |  |

| 3.4 | Form                                                          | ation of N-type Polycrystalline Silicon                                   | 102  |  |  |

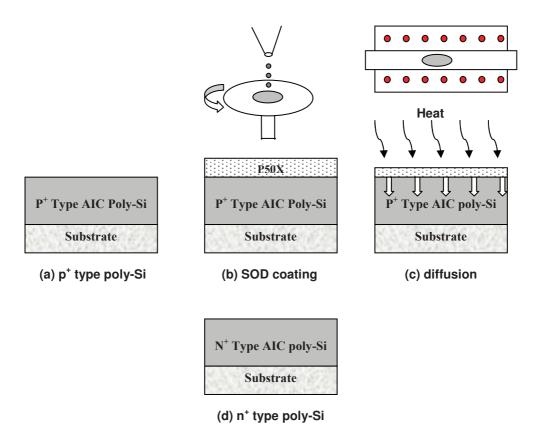

|     | 3.4.1                                                         | Ex-situ Doping of Polycrystalline Silicon                                 | 103  |  |  |

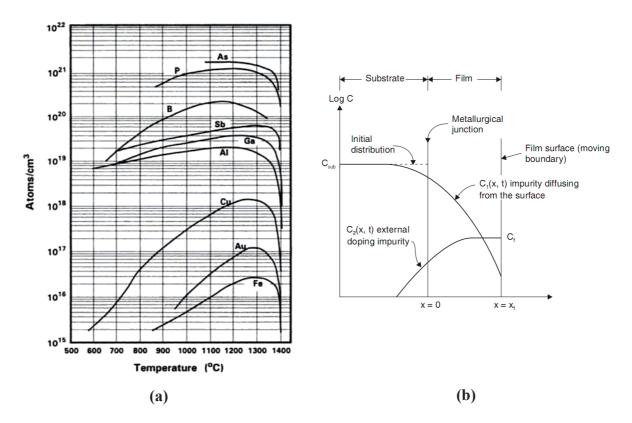

|     | 3.4.2                                                         | Formation of N-type Si by Phosphorus Doping of AIC Seed Layer             | 107  |  |  |

|     | 3.4.3                                                         | Electrical Properties of the N-type AIC Layers                            | 109  |  |  |

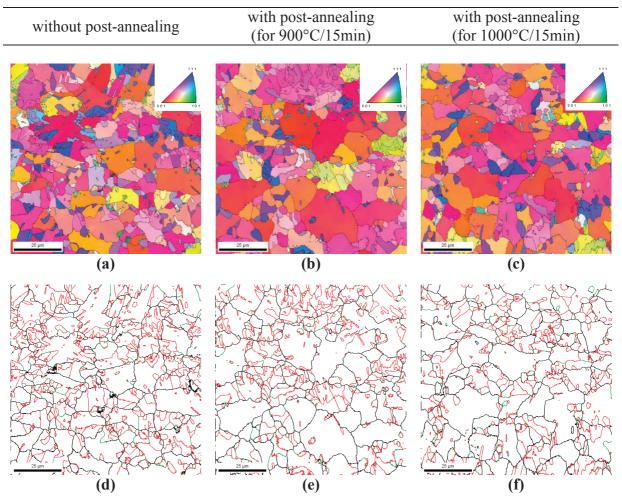

|     | 3.4.4                                                         | Effect of Post-Annealing for N-type AIC Seed Layer                        | 115  |  |  |

| REF | FEREN                                                         | CES                                                                       | 117  |  |  |

| СН  | APTER 4: PC                                          | LYCRYSTALLINE SILICON SOLAR CH                         | ELLS WITH   |  |

|-----|------------------------------------------------------|--------------------------------------------------------|-------------|--|

| AIC | C SEED LAYER                                         | APPROACH                                               |             |  |

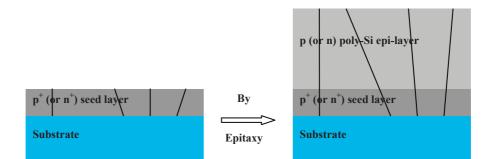

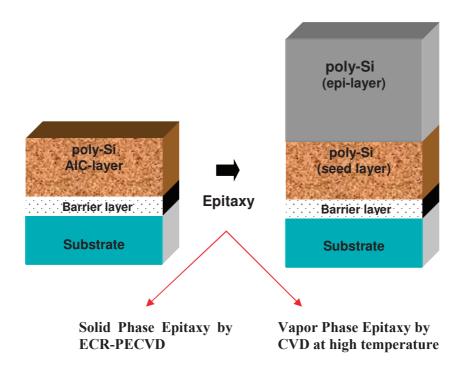

| 4.1 | Epitaxial Thicke                                     | ening on AIC Seed Layer                                |             |  |

|     | 4.1.1 Solid Phas                                     | e Epitaxy (SPE)                                        |             |  |

|     | i) Principle of                                      | SPE                                                    |             |  |

|     | ii) Experiment                                       | al procedure for SPE on AIC layer                      |             |  |

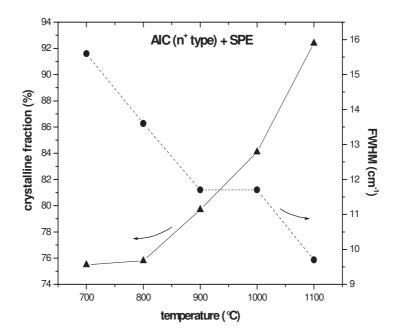

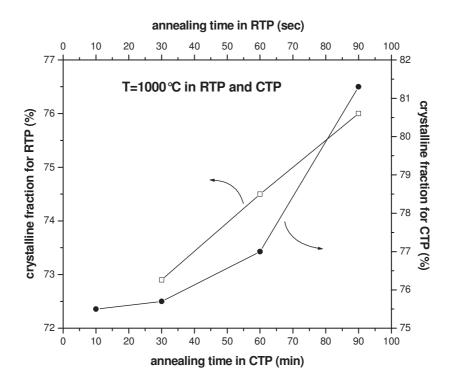

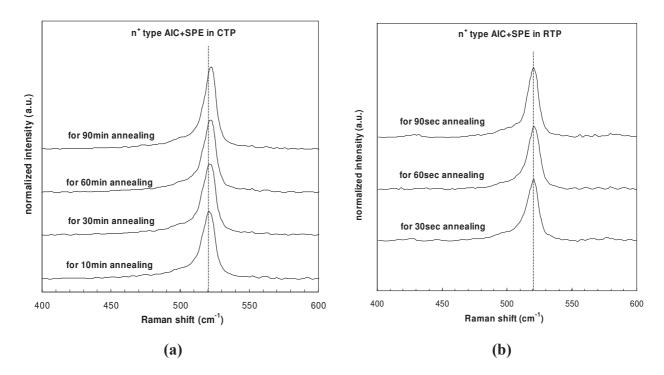

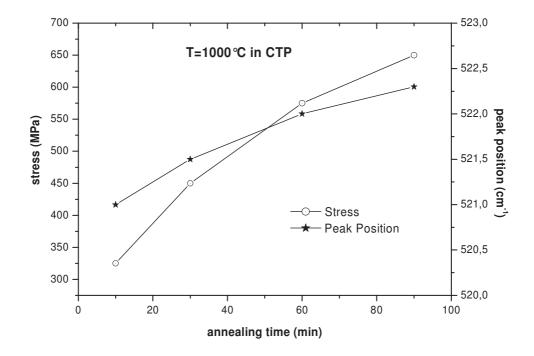

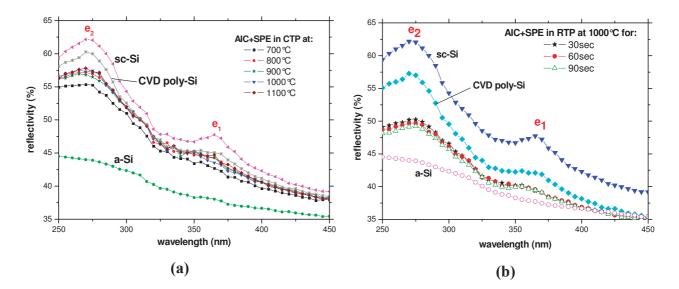

|     | iii) Structural                                      | properties of SPE films on AIC layers                  |             |  |

|     | iv) Crystallog                                       | aphic properties of SPE films on AIC layers            |             |  |

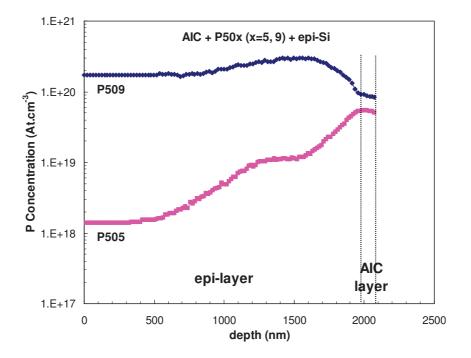

|     | v) Dopants dis                                       | tribution in SPE film on AIC layers                    |             |  |

|     | 4.1.2 Vapor Pha                                      | se Epitaxy (VPE)                                       |             |  |

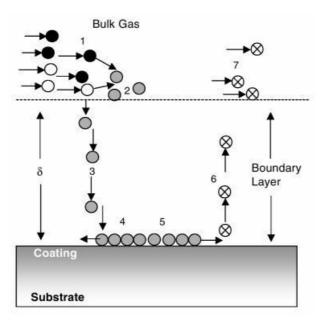

|     | i) Principle of                                      | VPE                                                    |             |  |

|     | ii) Experiment                                       | al procedure of VPE on AIC layers                      |             |  |

|     | iii) Structural                                      | analysis of the VPE-Si layers                          |             |  |

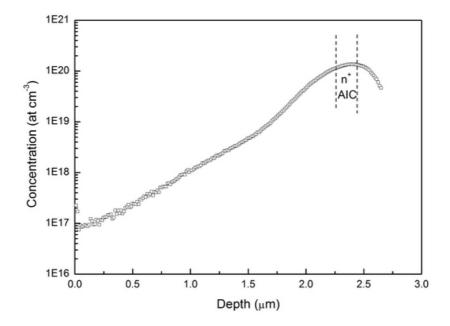

|     | iv) Dopants di                                       | stribution in VPE film on AIC layers                   |             |  |

| 4.2 | Thin Film Solar                                      | Cells Based on AIC Seed Layer                          |             |  |

|     | 4.2.1 Important                                      | Steps for Polysilicon Solar Cells                      |             |  |

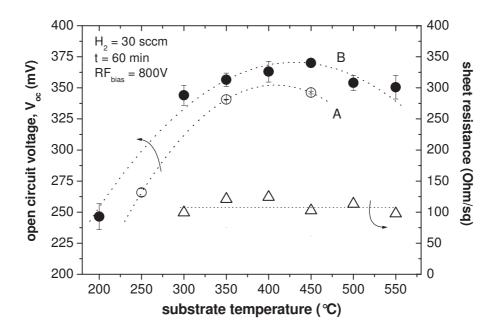

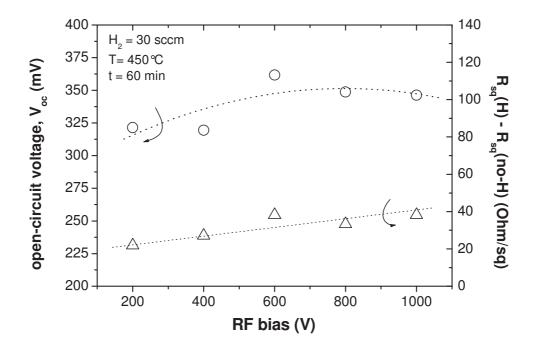

|     | i) Plasma hydr                                       | ogenation                                              |             |  |

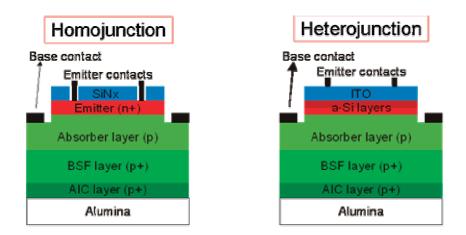

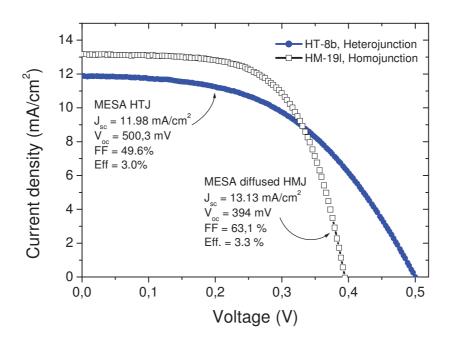

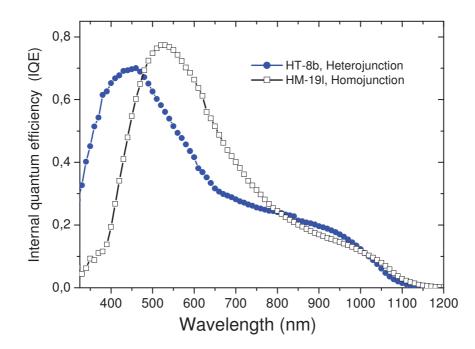

|     | ii) HMJ versu                                        | s HTJ emitter based solar cells                        |             |  |

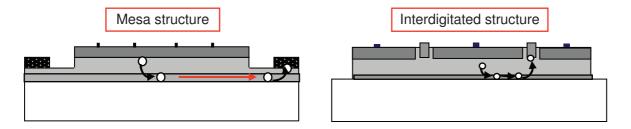

|     | iii) Mesa versus interdigitated contacts solar cells |                                                        |             |  |

|     | 4.2.2 Solar Cells                                    | s with AIC Seed Layer Approach                         |             |  |

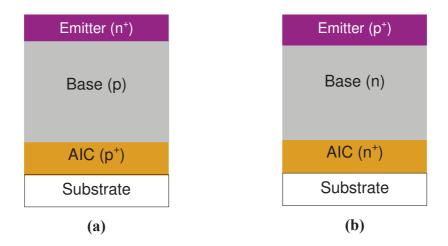

|     | i) Solar cell st                                     | ructures                                               |             |  |

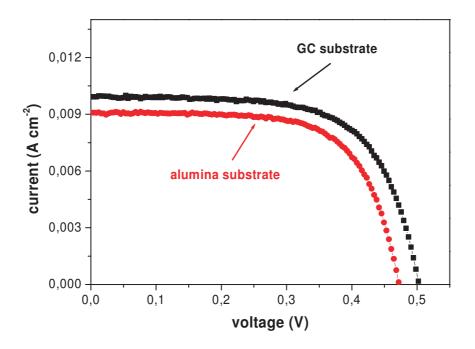

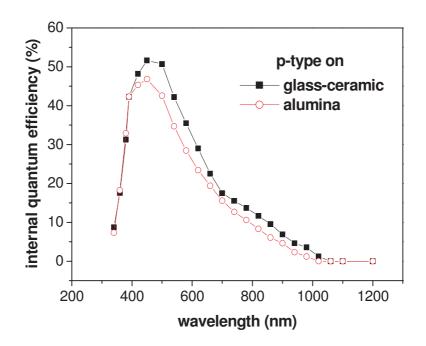

|     | ii) P-type base                                      | d polysilicon solar cells made on alumina and glass-ce | eramics 171 |  |

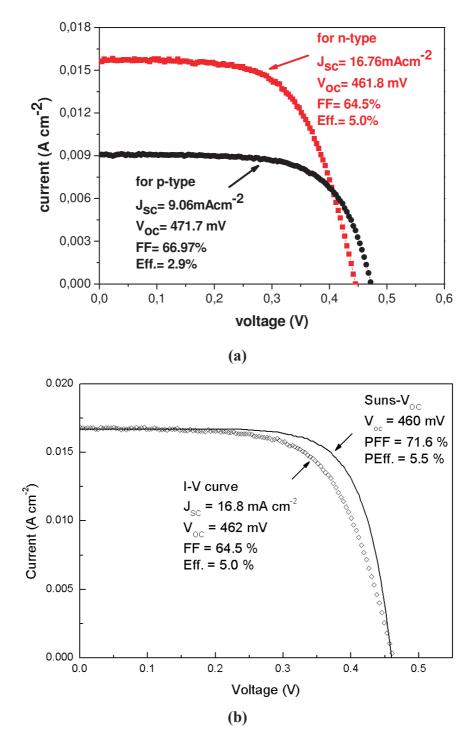

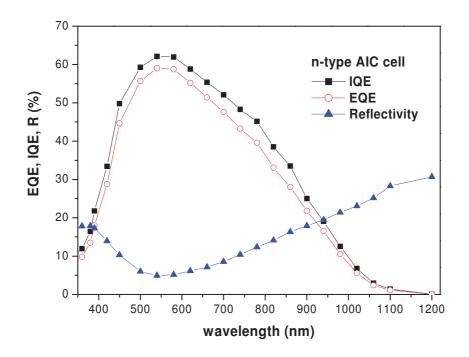

|     | iii) N-type bas                                      | ed polysilicon solar cells on alumina substrate        |             |  |

| REF | FERENCES                                             |                                                        |             |  |

| СН  | APTER 5: CO                                          | NCLUSION and OUTLOOK                                   |             |  |

|     |                                                      |                                                        |             |  |

|     |                                                      |                                                        |             |  |

|     |                                                      |                                                        |             |  |

|     |                                                      |                                                        |             |  |

| REF | FERENCES                                             |                                                        |             |  |

| LIS | T OF PUBLICA                                         | TIONS                                                  |             |  |

#### ABSTRACT

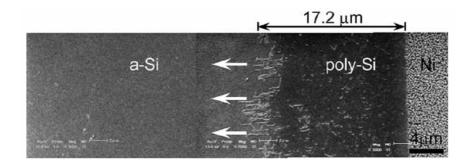

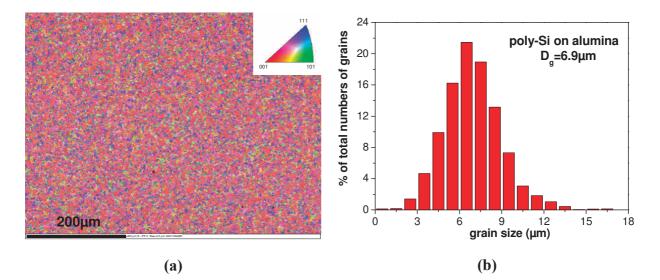

Thin-film polycrystalline-silicon (poly-Si) with a grain size between 0.1 and 100  $\mu$ m has triggered great interest in the field of photovoltaics as a promising alternative to silicon wafers and amorphous silicon (a-Si) thin films. Large grained p-type polysilicon films, 200nm thick, can be fabricated by aluminum-induced crystallization (AIC) of a-Si at temperatures below 500°C. In addition, n-type poly-Si thin films may present many advantages compared to p-type such as higher lifetime and better tolerance to defects.

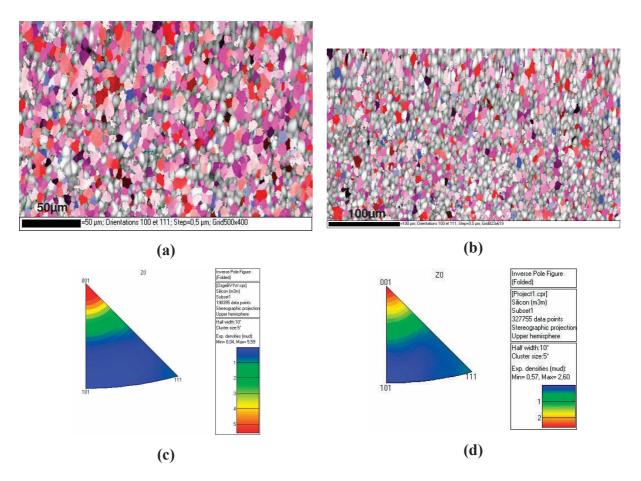

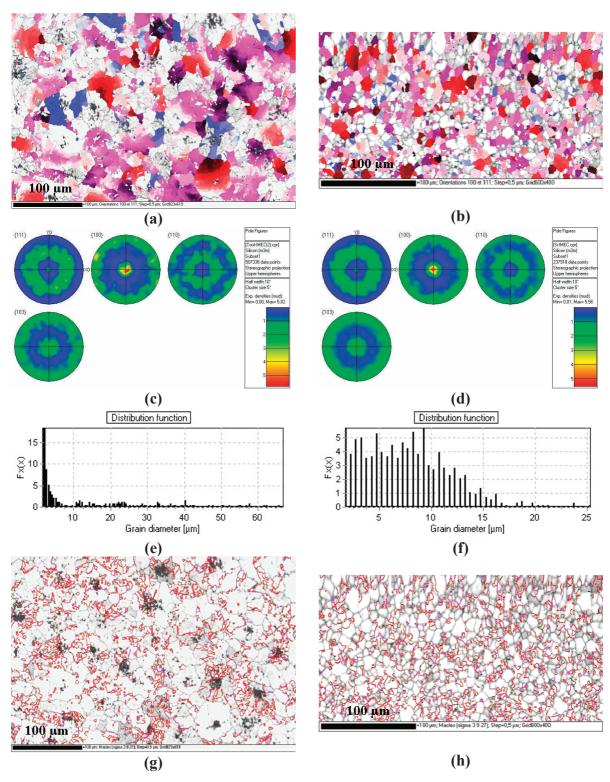

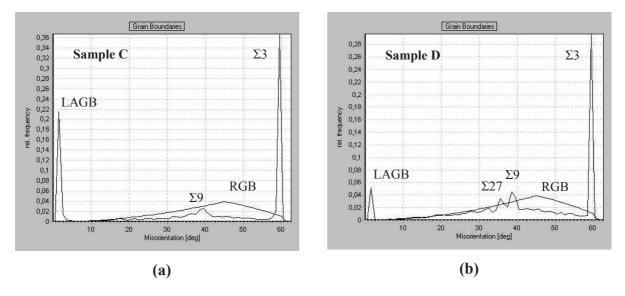

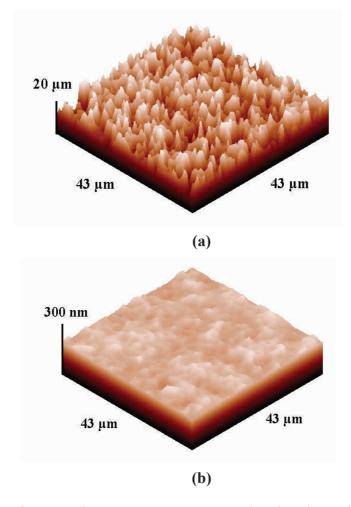

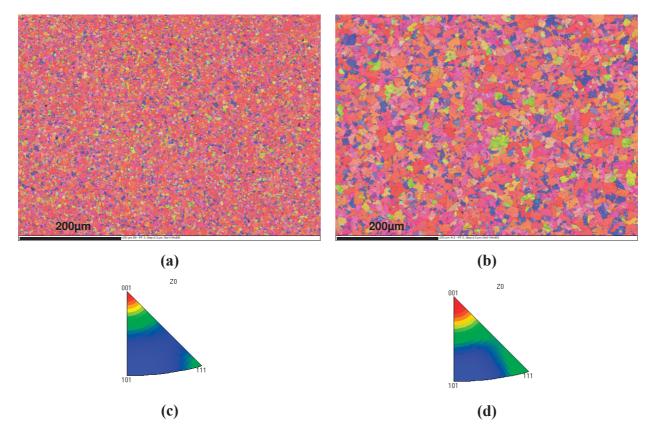

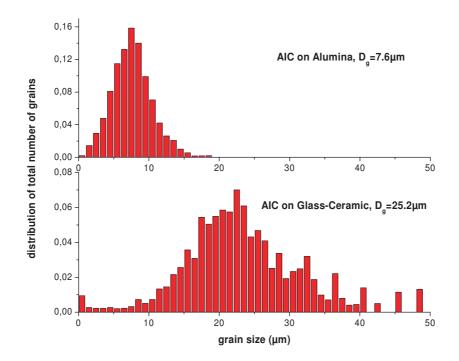

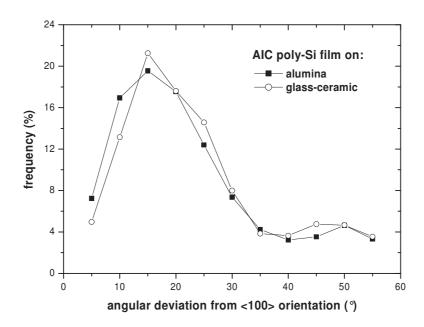

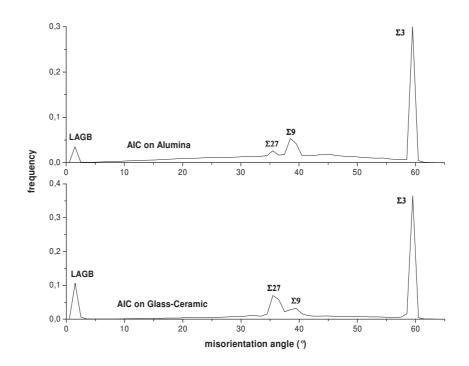

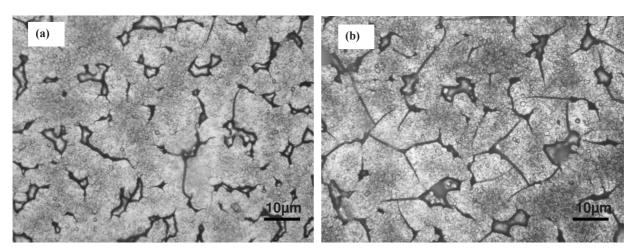

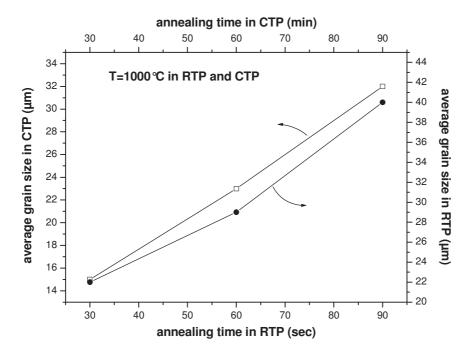

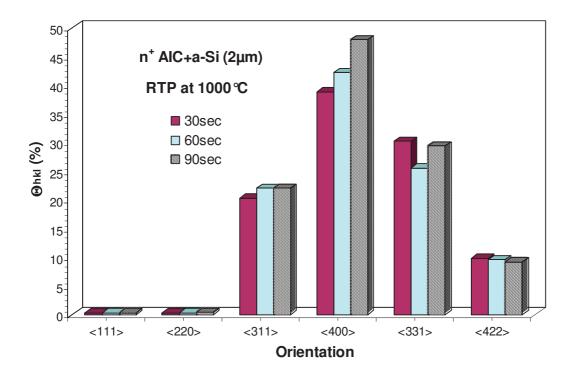

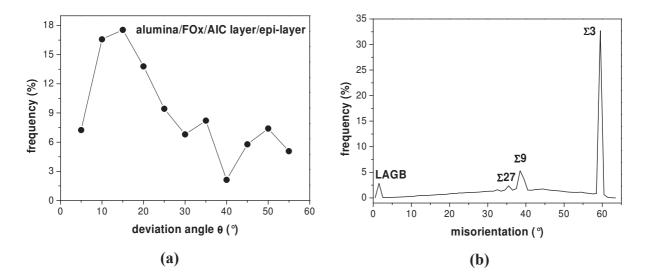

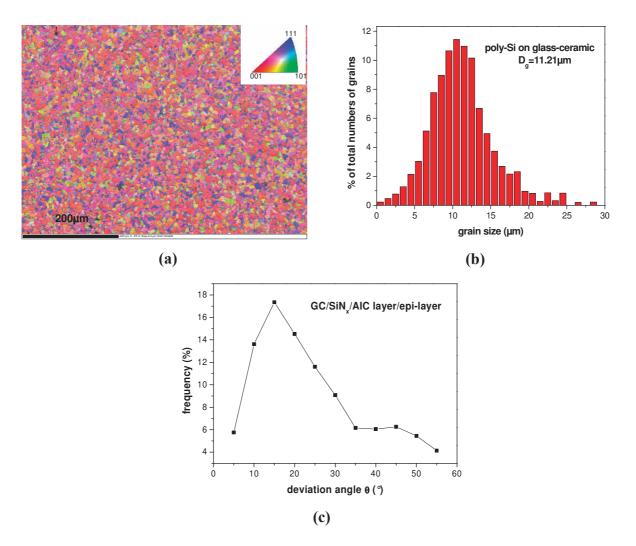

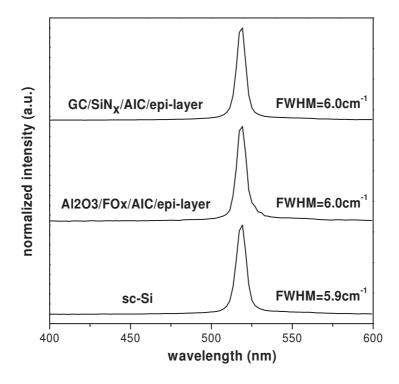

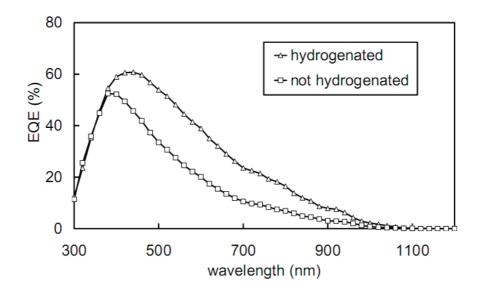

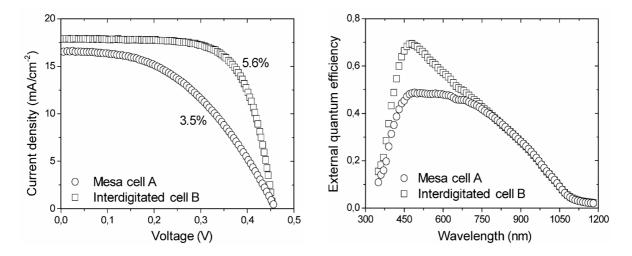

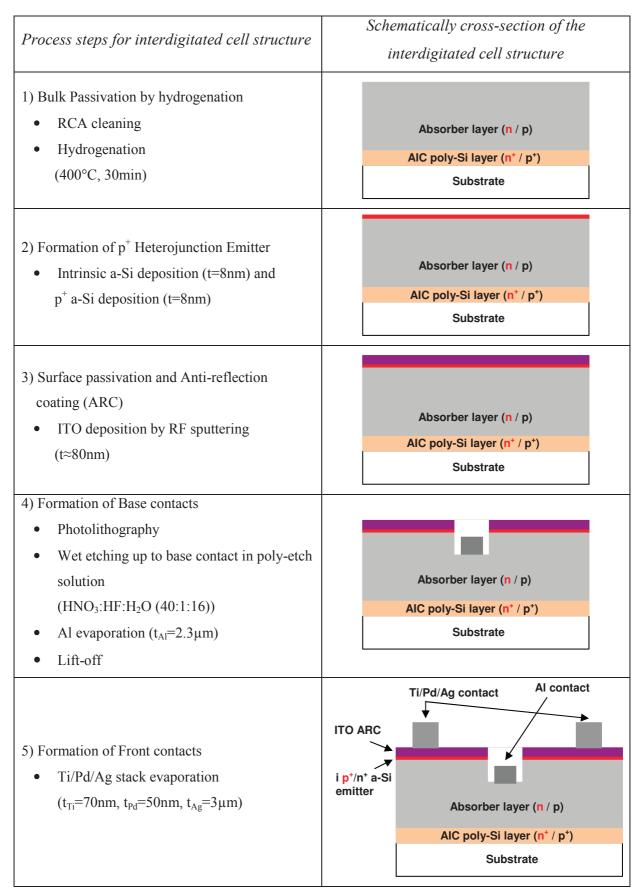

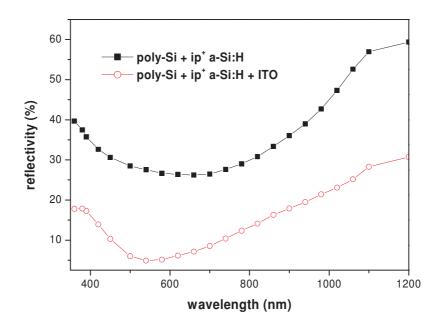

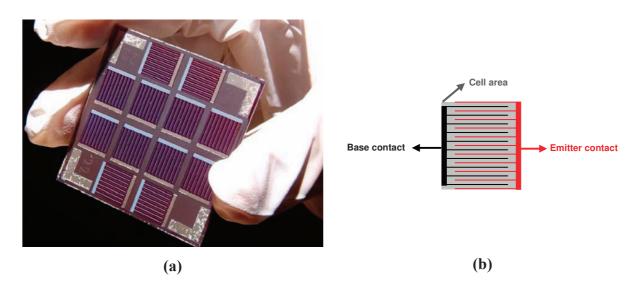

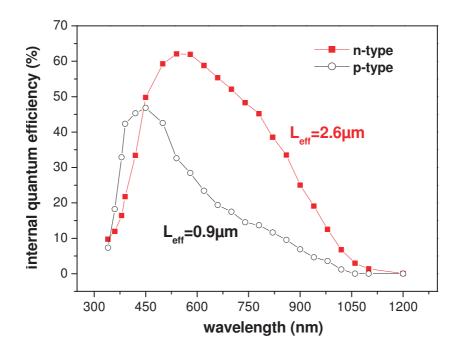

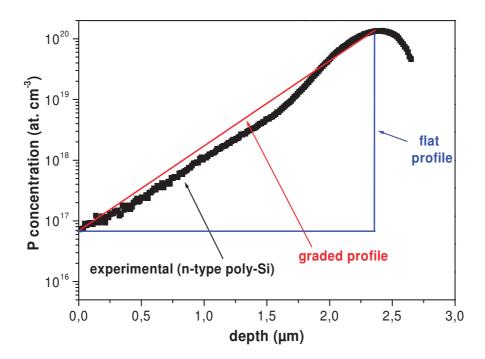

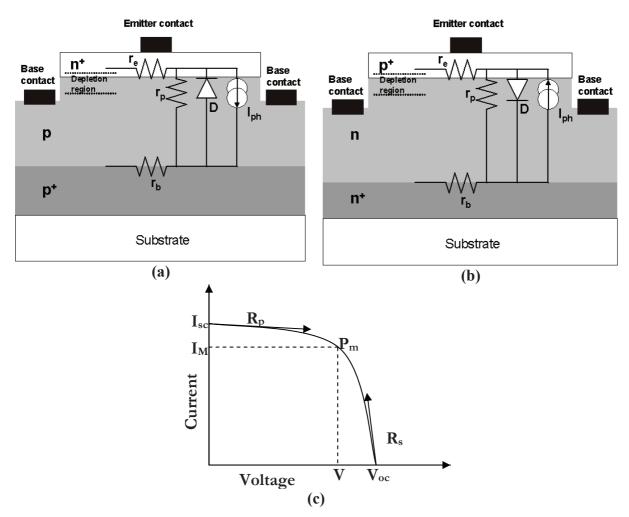

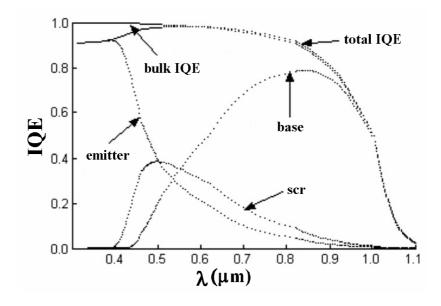

In this thesis, we have prepared p- and n-type poly-Si seed layers by AIC on alumina and glass-ceramic substrates, followed by epitaxial thickening using low pressure chemical vapor deposition (LPCVD); and HIT solar cells (Heterojunction with Intrinsic Thin layer) were then fabricated. The structural quality of the Si films was monitored by optical microscope and electron back scattering diffraction technique (EBSD). Polycrystalline silicon layer with quite large grains with an average grain size value of  $\sim 26 \mu m$  can be formed by AIC technique at 475°C on glass-ceramic substrate while it is only 7.6µm for AIC layer alumina substrate. While the surface roughness of susbtrate has a great influence on grain size, there is no effect on preferred orientation that is <100> for both types of samples. We have shown that the main crystallographic defects present in the continuous polysilicon layers are the lowangle grain boundary (LAGB, angle<2°) and the coincident site lattice (CSL) boundaries consisting of twin boundaries of first order ( $\Sigma$ 3), second order ( $\Sigma$ 9) and third order ( $\Sigma$ 27) while the majority of crystallographic defect is  $\Sigma 3$  independently from substrate choice. A graded doping profile was obtained by out-diffusion of phosphorus from the overdoped seed layer during the epitaxial thickening. The grain size conservation for epitaxial layer was observered with that of the underlying AIC poly-Si seed layer. We have also prepared for the first time n-type based polysilicon solar cells  $(n^+np^+)$  with AIC approach on alumina substrate. An efficiency of about 5.5% realized in our n-type cells without texturization that should be compared to 3.2% for p-type cells. In addition to cell efficiency, the spectral response of the n-type cell is also much widen than that of p-type cell, over a large part of the spectrum. This lead to an enhancement in  $L_{eff}$  for n-type cell (~2.6µm) compared to that of p-type (0.9µm). Analysis of the best n-type based cells with Sun-Voc apparatus, neglecting therefore the contacts resistivity, led to an efficiency value of 6.1%, showing the potential of the n-type polysilicon solar cells without any optimisation of the hydrogenation step, the heterojunction passivation and junction formation, nor the surface texturing. It is considered that this last step is capable to boost the efficiency by a factor a least of 2.

#### **RESUME DE THESE**

## Films de Silicium Polycristallin Obtenus par Cristallisation Induite par Aluminium et Epitaxie: Croissance, Caractérisations et Cellules Solaires

Parmi les orientations actuelles de recherche dans le domaine de la conversion photovoltaïque, il y'a l'émergence de cellules en couches minces (Si, CdTe, CIS). En particulier, l'utilisation de films minces en silicium polycristallin (<10 $\mu$ m d'épaisseur) déposés sur des substrats étrangers divers et peu coûteux (verre, céramique...) est aujourd'hui en pleine exploration car elle offre les avantages d'un faible coût et d'une grande stabilité. Il existe deux approche pour réaliser le film Si polycristallin (poly-Si) : (i) le dépôt direct par dépôt chimique en phase vapeur (CVD) à haute température (>1000°C) et temps court (<5min) ou la cristallisation en phase solide (SPC) d'un film de silicium amorphe à basse température (<500°C) mais pendant de longues heures (>24h). Dans ce cas, le film poly-Si présente des petits grains (1-3 $\mu$ m) avec une grande distribution, ce qui limite les performances par l'importante densité des joints de grains, (ii) la formation d'une couche poly-Si par cristallisation de silicium amorphe induite par métaux (MIC) ou par laser (LIC). L'objectif étant de réaliser une couche poly-Si à très gros grains, exemptes de défauts intra-grains et servant de couche « germe » ou tampon pour la formation d'une couche poly-Si plus épaisse par épitaxie.

Parmi les approches à couche tampon, il y a la formation du silicium polycristallin par le procédé de cristallisation du silicium amorphe induite par aluminium (AIC) qui permet de former une couche mince de silicium polycristallin (< $0.5\mu$ m) à larges grains (> $5\mu$ m) dopé à l'aluminium ( $2.10^{18}$  cm<sup>-3</sup>). La méthode consiste à recuire une bicouche a-Si/Al/substrat à des températures inférieures à l'eutectique ( $T_{eu} = 577^{\circ}$ C) pendant quelques heures. Durant le recuit, la structure initiale a-Si/Al/substrat permet d'inverser la structure en formant la couche poly-Si directement sur le substrat et l'excès d'aluminium n'ayant pas participé à la transformation se retrouve en surface de la structure et peut donc être facilement décapé. Une des clés de l'échange est la présence d'une couche d'oxyde d'alumine très fine entre les couches d'aluminium et de silicium amorphe, qui joue un rôle de membrane perméable. La couche poly-Si formée par la méthode AIC est trop mince (< $0.25\mu$ m) et fortement dopée de type p ( $\sim 2 \times 10^{18}$  Al/cm<sup>3</sup>). Elle ne peut pas servir comme matériau de base pour la conversion photovoltaïque. Ainsi, la couche AIC doit être épaissie par épitaxie à basse température ou à haute température. Le choix de la méthode d'épitaxie dépendra également du substrat choisit compte tenu de sa compatibilité avec les gaz utilisés et la température employée. Par ailleurs, il est établit que le silicium de type n pourrait présenter des avantages pour le rendement des cellules, notamment à cause de la grande mobilité des porteurs minoritaires et d'une plus grande tolérance aux défauts.

Dans ce travail, nous avons étudié d'abord la croissance du silicium polycristallin (couche germe AIC) sur substrats d'alumine ou vitrocéramiques par le procédé de cristallisation induit par aluminium du silicium amorphe. Les études ont concerné la cinétique de croissance de la couche AIC en fonction de plusieurs paramètres expérimentaux (température, temps, épaisseur du films Si amorphe, la teneur en hydrogène,...) et la détermination des défauts de structure inter-grains (joints) et intra-grains (macles). Nous avons également recherché à réaliser des films tampon de type n par surdopage et évaluer son efficacité. Nous avons étudié les propriétés structurales et opto-électroniques des couches épaisses silicium obtenues par épitaxie sur les couches tampon AIC. Nous avons utilisé deux méthodes de croissance de la couche absorbante: l'épitaxie en phase vapeur (VPE) à haute température ou l'épitaxie en phase solide (SPE) par dépôt d'une couche Si amorphe et recuit. Enfin nous avons réalisé des cellules photovoltaïques sur ces matériaux afin de valider leur potentiel pour la future génération de cellules solaires. Nous avons ainsi réalisé des structures de cellules de configuration  $n^+pp^+$  sur poly-Si de type p mais également des configurations  $p^+nn^+$  sur poly-Si de type n. La région « émetteur » des cellules a été réalisée soit par diffusion de dopants à partir d'une source solide, ou par dépôt d'une double couche ultra-fine de silicium amorphe l'une intrinsèque et l'autre fortement dopée. Ce travail s'inscrit en partie dans le cadre d'un projet national ANR intitulé POLYSIVERRE dans lequel les sociétés CORNING, AET, et TOTAL, et les académiques LPICM, INL et EMSE sont impliqués.

*Dans le premier chapitre*, nous avons présenté une étude bibliographique exhaustive nous permettant de poser les bases de la problématique du sujet traité. Cela a commencé par un rappel des différents matériaux et technologies photovoltaïques existantes à nos jours, leurs avantages et leurs inconvénients. Ensuite, nous avons abordé l'approche des couches minces pour le photovoltaïque, et plus particulièrement celle du silicium polycristallin sur substrat céramique qui fait l'objet de ce travail.

*Dans le deuxième chapitre*, nous avons rappelé les propriétés optiques et électroniques du silicium polycristallin, en relation avec la taille des grains, la densité des joints de grains et des défauts intra-grains. Ensuite, nous avons présenté les différentes méthodes -basse et haute température-utilisées pour former le silicium polycristallin. Nous avons largement détaillé les

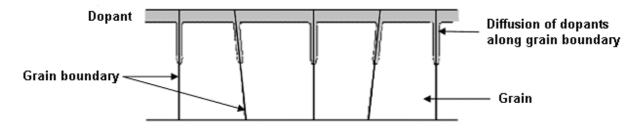

principes de la technique de cristallisation induite par métaux (MIC) du silicium amorphe, et en particulier le procédé de cristallisation induit par aluminium (AIC).

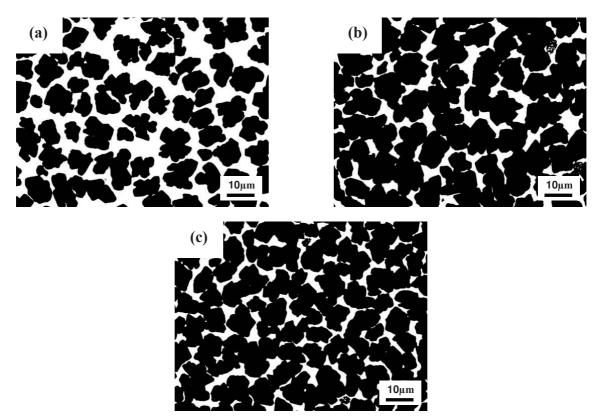

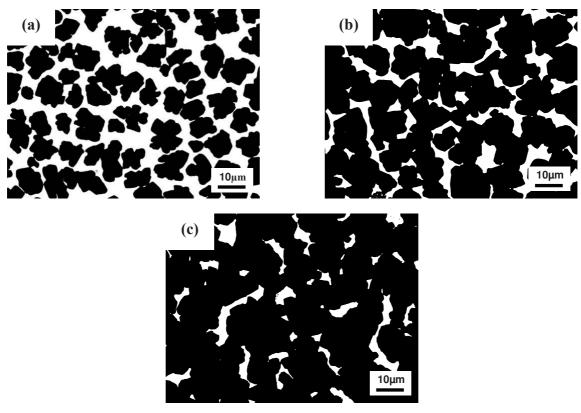

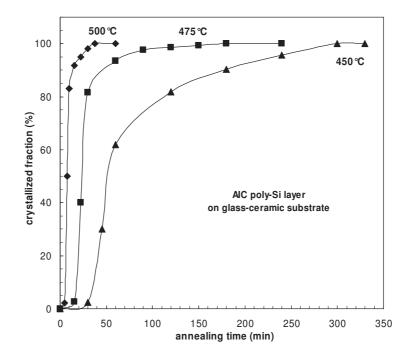

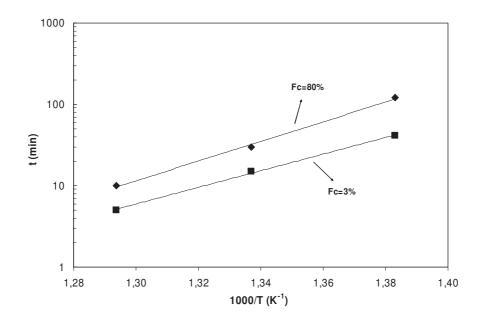

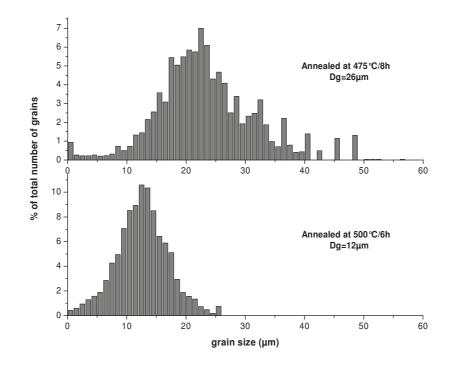

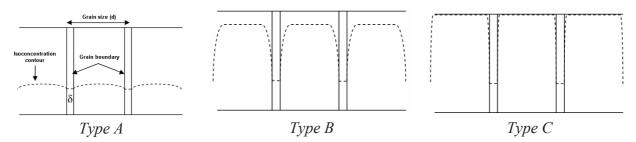

Le troisième chapitre présente nos résultats expérimentaux donnant les propriétés structurales, morphologiques et électriques des couches polycristallines de type p obtenues par le procédé AIC. En particulier, nous avons corrélé la cinétique de croissance aux paramètres techniques (température, temps) mais également au type de substrat céramique utilisé : alumine ou verre haute température. Grâce à des observations optiques et à des analyses EBSD (Electron Back-Scattered Diffraction), nous avons déterminé la distribution de la taille des grains, la densité des joints de grains et la densité des macles. Nous avons suivi l'évolution de ces différentes grandeurs en fonction de traitements thermiques postérieurs au procédé AIC pour suivre l'évolution de la cristallographie des grains. En utilisant des verres céramiques, nous avons pu réaliser des films poly-Si à T<500°C, présentant une taille moyenne de grains cent fois supérieure à son épaisseur ( $0.2\mu$ m d'épaisseur et 26 $\mu$ m en taille des macles, en particulier  $\Sigma$ 3, est réduite en diminuant la température de cristallisation. Les raisons de ce comportement sont largement discutées.

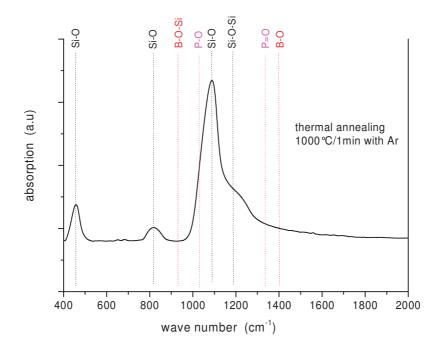

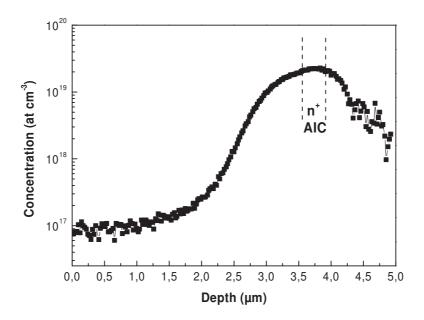

Une partie de chapitre concerne également la transformation des films silicium AIC de type P (P-AIC) en matériau de type n (n-AIC) par diffusion à partir d'une solution siliçeuse contenant du phosphore. En variant les conditions expérimentales, des couches N<sup>+</sup> avec des concentrations de porteurs libres de  $10^{19}$  à  $6 \times 10^{20}$  cm<sup>-3</sup> et des mobilités de 50-60 cm<sup>2</sup>/Vs ont pu être réalisées sur des couches de  $0.2 \mu$ m. Le dopage élevé de cette couche est essentiel pour assurer un champ arrière efficace, et également comme source de dopants lors de la croissance épitaxiale sur cette couche n-AIC.

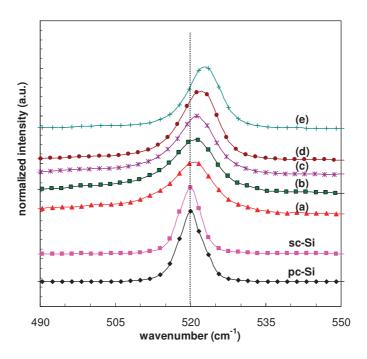

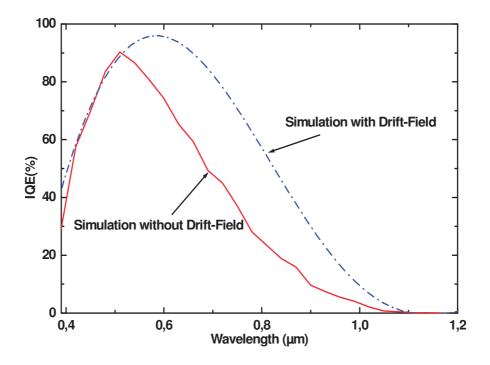

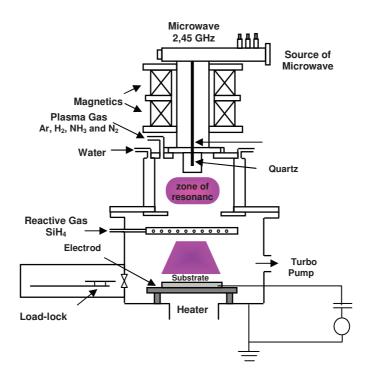

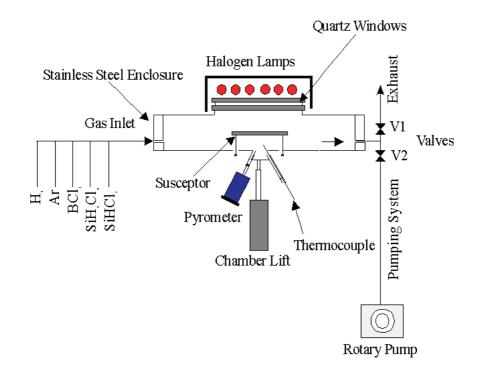

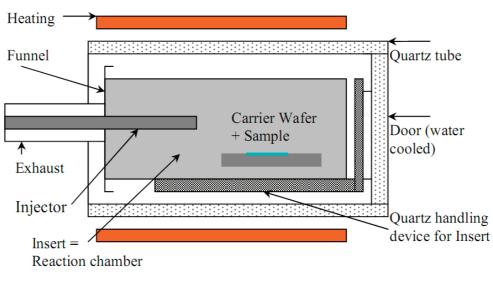

**Dans le chapitre 4**, nous décrivons les deux méthodes de croissance de couches épaisses sur nos films p-AIC et n-AIC par épitaxie. L'épitaxie en phase solide a consisté dans le dépôt d'un film de silicium amorphe de  $2\mu$ m d'épaisseur par CVD assisté par micro-onde (MW-CVD) suivi d'un recuit thermique conventionnel ou rapide (à lampes halogènes) mais à haute température (>900°C). Nous avons montré que la présence d'une grande concentration d'hydrogène dans la couche amorphe, qui exo-diffuse lors du recuit, ne permettait pas d'obtenir une bonne épitaxie. Par opposition, l'épitaxie en phase vapeur (VPE) consistant à craquer SiH<sub>4</sub> ou SiH2Cl<sub>2</sub> à haute température (>900°C) a permis d'obtenir des couches épitaxiales de très bonne qualité cristallographique. Grâce à des observations de morphologie et des analyses en micro-Raman, nous avons pu identifier également le taux de contraintes dans les couches en fonction des conditions d'épitaxie. Nous avons également suivi l'évolution

du dopant (aluminium, phosphore) dans les couches épitaxiales par SIMS ou par mesures électriques. Nous avons ainsi pu mettre en évidence la formation d'une distribution graduelle  $n^+n$  très souhaitable pour les composants photovoltaïques.

La deuxième partie du chapitre 4 est consacrée aux cellules photovoltaïques tests, afin de tester la potentialité de tels matériaux pour une conversion efficace de l'énergie solaire. En particulier, les premières cellules réalisées sur des couches poly-silicium à base de p-AIC ont montré des rendements de 2.8% et 3.3% sur substrats d'alumine ou verre céramique. Comme attendu, nous avons mesuré un rendement de l'ordre de 5.5%, pour les cellules préparées par VPE sur couche tampon n-AIC. Il faut rappeler qu'aucun confinement optique ni architecture spécifique n'a été utilisé. Les caractéristiques impliquant les mesures des différentes grandeurs des cellules et la réponse spectrale, ont permis une analyse fine des régions de pertes de la conversion. Ces résultats photovoltaïques sont largement discutés en relation avec les propriétés des matériaux, et les améliorations sont proposées.

# **CHAPTER 1: INTRODUCTION**

### 1.1 PHOTOVOLTAIC ENERGY SOURCE

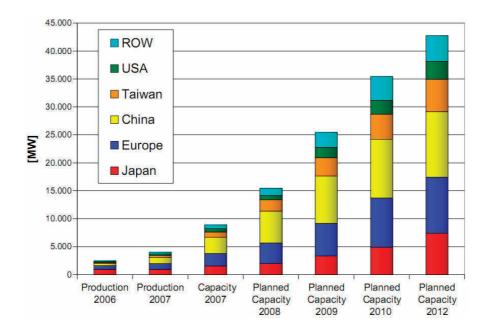

Since 2003, total PV production grew in average by almost 50%, whereas the thin film segment – starting from a very low level – grew in average by over 80% and reached 400MW or 10% of total PV production in 2007. Production data for the global cell production in 2007 vary quite significantly between 3.733MW and 4.279MW (Figure 1.1) [1]. The Photovoltaic world market grew in terms of production by more than 60% in 2007 to approximately 4GW. The market for installed systems also grew more than 60% to reach 2.825MW. Like in the last years, Germany was the largest single market with 1.100 MW, followed by Spain with 341MW, Japan with 210MW and the US with 205MW.

Figure 1.1: Worldwide PV Production 2006/7 and planned production capacity increases [1].

The Photovoltaic Energy Barometer reported that Europe had a cumulative installed PV system capacity of 4.7GW in 2007. Despite the fact that the European PV production grew again by almost 60% and reached 1040MW in 2007 while the Japanese market saw a further decline to 210 MW of new installations, 36% lower than in 2006. Then in 1998, progressive and supportive government policies in many European countries and in Japan resulted in a substantial increase in production. These policies were driven partly by a strong commitment to  $CO_2$  reduction as proscribed by the Kyoto Protocol. Figure 1.1 shows the

announced and estimated increase of production capacities by 2006/7. Besides the exponential increase of the world market, the even more rapid increase of the Chinese production capacities is of particular interest. If the announced production increases can be realized, China will represent about 27% of the worldwide 42.8GW. Europe will then be second with almost 23% and Japan third with 17%.

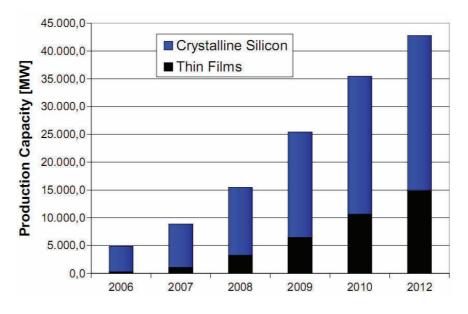

About 90% of the current production uses wafer-based crystalline silicon technology. Up to now the main advantage of this technology was that complete production lines could be bought, installed and be up and producing within a relatively short time-frame. However, the ongoing shortage in silicon feedstock and the market entry of companies offering turn-key production lines for thin film solar cells led to a massive expansion of investments into thin film capacities. Thin film segment, starting from very low level, grew by almost 80% and reached 400MW or 10% of total PV production in 2007. The high growth rate of thin film production and the increase of the total production share indicate that the thin film technology is gaining more and more acceptance. For 2010, roughly 10.5GW of thin film production capacities are announced, an increase of almost 4GW compared to the 2009 figures. A thin film market share of 25 to 30% in 2010 seems not to be unrealistic. This takes into account the fact that more and more PV manufacturers are diversifying their production portfolio and that the current market leader First Solar will reach an annual production capacity of more than 1GW by 2010 [1]. Should the announced increases be realized, total production capacities in 2012 could then stand at 42.8GW, of which 15GW could be thin films as shown in Figure 1.2.

Figure 1.2: PV Production Capacities 2006 and planned production capacity increases [1].

The current solar cell technologies are well-established and provide a reliable product, with sufficient efficiency and energy output for at least 20 years of lifetime. This reliability, the increasing potential of electricity interruption due to grid overloads, as well as the rise of electricity prices from conventional energy sources, add to the attractiveness of Photovoltaic systems.

#### **1.2 PHOTOVOLTAIC MATERIALS & TECHNOLOGIES**

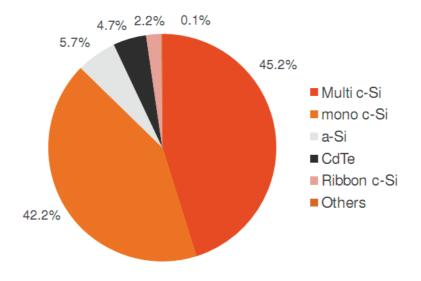

New products have been entering the market, enabling further cost reduction. Equally competitive technologies are amorphous/micromorph Silicon, CdTe and Cu(In,Ga)(S,Se)<sub>2</sub> thin films. In addition, dye-cells are getting ready to enter the market as well. The growth of these technologies is accelerated by the positive development of the PV market as a whole. The technology as well as the company distribution varies significantly as shown in Figure 1.3. The majority of 47 companies is silicon based. And year to year thin film production capacity increases.

#### 1.2.1 Bulk Silicon Solar Cells

Figure 1.3 shows that c-Si, as either single or multicrystalline wafers or ribbons or amorphous Si/c-Si (heterojunction cells), was responsible for more than 90% of worldwide PV production in 2007. How did its dominance occur? First, there was a tremendous worldwide scientific and technical infrastructure for Si starting in the 1960s. Huge government and industrial investments were made in programs for understanding the chemical and electronic properties of Si, how to grow it with the required purity and crystalline structure, and to create the equipment needed to perform all the processing steps. The silicon band gap, of 1.1eV, is almost optimum to make a good solar converter. In addition, Si is one of the most abundant minerals in the Earth's crust. Thus, there was no physical limitation to providing a huge fraction of the Earth's electricity needs with the known Si reserves. However, for mechanical reasons (it is brittle), silicon requires relatively thick cells, with a typical wafer thickness of about 300µm. Therefore, some of the electrons pumped by the photons to the conduction band have to travel large distances, on the order of the thickness. Consequently, a good material with high chemical purity and structural perfection is required to fight the natural tendency of the conduction-band electrons to return to the valence band which is recombination. To process high-quality Si wafers, hightemperature treatments (>800°C) for the formation of pn junction, the anti-reflection layer

coating and the annealing of the contacts are necessary processes. The wafers are saw out of an ingot obtained by the float zone (Fz) or Czochralski (Cz) extrusion process for single crystalline, or by solidification for multicrystalline silicon materials.

Figure 1.3: Cell technology market shares in 2007 [2].

An efficiency of 24.7% in UNSW has been achieved for single-crystal silicon laboratory cells in a long complex process where every possible efficiency-improving detail has been implemented to produce a complicated but nearly ideal device structure. However, most factories use some variation of the wafer and cell fabrication process, including the screen-printing process, which leads to 15% single crystal cells or 13% multicrystal cells. In modules, these efficiencies are reduced to 14% or 12%, mainly due to the redefinition of area that now includes the module frame. This process is considered the best compromise between costs and performance. The existence of the large efficiency gap between laboratory and commercial cells, together with the increasing markets, suggest that novel, high efficiency commercial cell processes will appear in the next years. Some companies (BP Solar or Sanyo, for instance) are already on this path and have different processes leading to 17 to 18% cells in production. The costs distribution for the industrialist is approximately 50% for material, 30% for setting in module and 20% for the processes of development of the cells [3]. The lowest (publicly offered) module selling prices in 2002 were about 3\$/Wp. The wafer itself represents about 65% of the module cost, approximately equally divided between purification, crystallization, and sawing. An important advance in solar cell fabrication was the demonstration that solar cells with high efficiency can be fabricated from wafers containing hundreds of large-grain (1-10mm) multicrystals, called multicrystalline (multi-Si) or

polycrystalline (poly-Si), although this later term is less favored because it may cause confusion with the feedstock (polysilicon). The multi-Si growth procedure is much faster and the wafer is cheaper.

The loss of efficiency of a few percent (absolute) caused by the random orientation of crystalline grains in a multi-Si wafer compared to a single c-Si wafer is balanced by the lower cost so that the price per watt peak is the same on a module basis. But the simplicity of the multi-Si wafer-growing equipment and process is producing a clear trend towards the use of the multicrystalline option.

An interesting option in Si solar cell manufacturing is the growth of ribbons [4]. Ribbons do not require the expensive sawing process. However, the growth of the ribbon crystal is slower because they usually grow in the plane perpendicular to the ribbon surface, with very small area (the ribbon width times the thickness). In contrast, wafers grow in the plane of the wafer surface whose area is the wafer area. The standard ingot solidification process is a very effective purification process due to the preferential segregation of impurities to the molten silicon. However, in ribbon Si the plane of solidification moves faster (although with very small area), so the segregation is less effective. In summary, the ribbon cells are almost as good as the multicrystalline bulk-grown cells and possibly cheaper. Challenges lie in increasing the growth speed and the resulting cell efficiency.

In good single crystal Si cells, the manufacturing yield is 95%. Many supposedly cheap technologies find their Achilles' heel in the low yield. Finally, the module fabrication requires interconnecting and encapsulating the cells. These steps also have room for some cost reduction. The use of cheaper materials may help somewhat, as well as better automation, better module interconnection, and integration designs.

### 1.2.2 Thin Film Compound and Organic Solar Cells

#### a. Thin film compound solar cells:

Today's mainstream PV technology is based on crystalline Si wafers. This is robust and proven PV technology, however, its cost reduction potential seems limited. Due to greatly reduced semiconductor material consumption and ability to fabricate the solar cells on inexpensive large-area foreign substrates and to monolithically series-connect the fabricated cells, thin film PV has the potential of achieving module fabrication costs of well below 1€/Wp [5]. When Si is so well established a totally different semiconductor technology for photovoltaics are developed to achieve lower cost and improved manufacturability at larger scales than could be envisioned for Si wafer-based modules. The c-Si that led to the early investigation and eventual commercialization of alternatives has the disadvantages since Si crystals were expensive and slow to grow. It was also recognized that of all the viable semiconductors, Si would require the greatest thickness to absorb sunlight, due to its unique optical properties. Si is the most weakly absorbing semiconductor used for solar cells because it has an indirect band gap while most of the other semiconductors have a direct band gap. Therefore, at least ten times more crystalline Si is needed to absorb a given fraction of sunlight compared to other semiconductors like GaAs, CdTe, Cu(InGa)Se<sub>2</sub>, and even other forms of Si such as a-Si. Thicker semiconductor material means higher material volume, but also a higher quality material because of the longer paths that the high-energy electrons excited by the photons must travel before they are delivered to the external circuit to produce useful work. All this leads to high material cost.

The main advantage of thin film solar cells (TFSC) is that they will eventually have lower costs than c-Si-wafer PV technology when they are produced in sufficiently large volumes to off-set the initial capital investment. The lower costs of TFSC derive from the following characteristics: they are typically 100 times thinner than Si wafers ( $\sim 1-3\mu$ m for all the semiconductor layers) deposited onto relatively low-cost substrates such as glass, metal foils, and plastics; they are deposited continuously over large areas at much lower temperature (200 to 500°C vs  $\sim 1400$ °C for c-Si); they can tolerate higher impurities (thus needing less expensive purification of raw materials); and they are easily integrated into a monolithic interconnected module. For a reference, the semiconductors in typical TFSC are 10 times thinner than a human hair. TFSC are either polycrystalline with small  $\sim 1\mu$ m sized grains such as Cu(InGa)Se<sub>2</sub> or CdTe, or else amorphous like a-Si. TFSCs typically consist of 5 to 10 different layers whose functions include reducing resistance, forming the pn junction, reducing reflection losses, and providing a robust layer for contacting and interconnection between cells.

The materials based on CuInSe<sub>2</sub> that are of interest for photovoltaic applications include several elements from groups I, III and VI in the periodic table. These semiconductors are especially attractive for TFSC application because of their high optical absorption coefficients and versatile optical and electrical characteristics which can in principle be manipulated and tuned for a specific need in a given device. CIS is an abbreviation for general chalcopyrite films of copper indium selenide (CuInSe<sub>2</sub>), CIGS mentioned below is a variation of CIS. CIS films (no Ga) achieved greater than 14% efficiency. However, manufacturing costs of CIS solar cells at present are high when compared with amorphous silicon solar cells

but continuing work is leading to more cost-effective production processes. The first largescale production of CIS modules was started in 2006 in Germany by WURTZ Solar. Manufacturing techniques vary and include the use of Ultrasonic Nozzles for material deposition. Electro-Plating in other efficient technology to apply the CI(G)S layer.

When gallium is substituted for some of the indium in CIS, the material is referred to as CIGS, or copper indium/gallium diselenide, a solid mixture of the semiconductors CuInSe<sub>2</sub> and CuGaSe<sub>2</sub>, often abbreviated by the chemical formula CuIn<sub>x</sub>Ga<sub>(1-x)</sub>Se<sub>2</sub>. Unlike the conventional silicon based solar cell, which can be modelled as a simple pn junction, these cells are best described by a more complex heterojunction model. The best efficiency of a thin-film solar cell as of March 2008 was 19.9% with CIGS absorber layer for small cells [6]. However, the technology has proved difficult to commercialise. The best commercial modules are presently 11-13% efficient. Higher efficiencies (around 30%) can be obtained by using optics to concentrate the incident light or by using multi-junction tandem solar cells. The use of gallium increases the optical bandgap of the CIGS layer as compared to pure CIS, thus increasing the open-circuit voltage, but decreasing the short circuit current. In another point of view, gallium is added to replace indium due to gallium's relative availability to indium. Approximately 70% of indium currently produced is used by the flat-screen monitor industry. However, the atomic ratio for Ga in the >19% efficient CIGS solar cells is ~7%, which corresponds to a bandgap of ~1.15eV. CIGS solar cells with higher Ga amounts have lower efficiency. For example, CGS solar cells, which have a bandgap of  $\sim 1.7 \text{eV}$ , have a record efficiency of 9.5% for pure CGS and 10.2% for surface-modified CGS. The main technical issue of the CIS technology is associated with the complexity of the CIS absorber layer (a 5element system), which imposes significant challenges for the realisation of uniform film properties across large-area substrates using high-throughput equipment. This affects the yield and the cost (€/Wp) of the modules. Other issues are the use of cadmium (as previously noted) and the use of the scarce element indium. Estimates indicate that all known reserves of indium would only be sufficient for the production of a few GWp of CIS PV modules [5].

Polycrystalline layers of CdTe have been investigated for photovoltaics since the 1970s. A CdTe solar cell is a solar cell based on CdTe, an efficient light-absorbing material for thin-film cells. Compared to other thin-film materials, CdTe is easier to deposit and more suitable for large-scale production. The pn junction is formed by first depositing an n-type layer of CdS on a transparent conductive oxide substrate followed by the CdTe layer and appropriate chemical annealing. Once the solar cell is made, the CdTe films are slightly p-type, typically, 2 to 8µm thick and have crystallites or grains on the order of 1µm. The highest

reported efficiency for solar cells based on thin films of CdTe is 18%, which was achieved by research at Sheffield Hallam University for small-area cells while the best commercial modules are presently 10-11% efficient. The main technical issue of the CdTe technology is related to the back contact. Specifically, the relatively light p-type doping of the CdTe layer complicates the realisation of a low-resistance, long-term-stable back contact. The standard method for realising the back contact structure of CdTe solar cells presently consists of chemical etching of the CdTe surface, followed by the deposition of a p<sup>+</sup>-type buffer layer and then the metal film [7]. Another technical issue is the activation step, which involves a toxic atmosphere and thus should be modified or eliminated. The main issue of the CdTe PV technology, however, is related to the toxicity of Cd. Even if proper recycling of the modules is offered by the module manufacturers, it is questionable whether the production and deployment of Cd-based modules is sufficiently benign environmentally to justify their use instead of less problematic PV technologies. Furthermore, Te is a scarce element and hence, even if most of the annual global Te production is used for PV, CdTe PV module production seems limited to levels of a few GWp per year [5].

#### b. Organic solar cells:

Organic solar cells and Polymer solar cells are built from thin films (typically 100nm) of organic semiconductors such as polymers and small-molecule compounds like polyphenylene vinylene, copper phthalocyanine (a blue or green organic pigment) and carbon fullerenes and fullerene derivatives such as PCBM. Energy conversion efficiencies achieved to date using conductive polymers are low compared to inorganic materials, with the highest reported efficiency of 6.5% for a tandem cell architecture. However, these cells could be beneficial for some applications where mechanical flexibility and disposability are important.

These devices differ from inorganic semiconductor solar cells in that they do not rely on the large built-in electric field of a pn junction to separate the electrons and holes created when photons are absorbed. The active region of an organic device consists of two materials, one which acts as an electron donor and the other as an acceptor. When a photon is converted into an electron hole pair, typically in the donor material, the charges tend to remain bound in the form of an exciton, and are separated when the exciton diffuses to the donor-acceptor interface. The short exciton diffusion lengths of most polymer systems tend to limit the efficiency of such devices. Nanostructured interfaces, sometimes in the form of bulk heterojunctions, can improve performance. Additionally, the operational lifetime of organic solar cells must be improved to extend beyond 5 years.

8

#### 1.2.3 Thin Film Silicon Solar Cells

A major cost limitation of the current dominant silicon solar cell technologies, which are fabricated using traditional monocrystalline and multicrystalline silicon based processes, is with the large volume of material used and the associated expensive assembly and interconnection methods required to produce the large area products required for substantial power generation. Thin-film 'coating' technologies, which avoid these problems, have achieved substantially lower manufacturing costs, but market acceptability has been compromised by the much lower power conversion efficiencies achieved so far.

Thin-film approaches aim to reach low cost by starting with a low-cost (or potentially low-cost) material system; a thin layer of semiconductor is deposited on a low-cost substrate. If high efficiency and reliability is indeed achieved, thin-film solar cell technologies could reach substantially lower costs, 0.5\$/Wp and even below. Although thin-film solar cells have been announced for a long time as the next best thing, they have not yet had a breakthrough. The development of these technologies has in fact been rather slow, not faster than the bulk Si technology which, however, started much earlier. Recently, because of the Si feedstock shortage, the thin-film technologies have received new momentum. Because of the limited possibility to invest in conventional Si technology due to the shortage, substantial investment capital has flown into thin-film initiatives and led to the creation of many new companies [8].

Using Si for the active material instead of other semiconductors presents a number of advantages for thin-film technologies. Si is nontoxic, which makes it easily accepted by the public. Moreover, Si is abundantly available in the earth crust, so that its availability (at least in its raw form) will never be an issue. Finally, Si solar cell technologies can build further upon the extensive know-how accumulated over the years in the IC industry (for crystalline Si) and the display industry (for amorphous and microcrystalline Si). The term "thin-film crystalline Si" is in fact quite broad. It covers a wide range of technologies, from amorphous Si to monocrystalline lift-off Si solar cells.

Thin silicon solar cells is actually an umbrella term describing a wide variety of silicon photovoltaic device structures utilizing various forms of silicon (monocrystalline, multicrystalline, polycrystalline, microcrystalline, polymorphous, amorphous), and made with an almost incredibly diverse selection of deposition or crystal growth processes and fabrication techniques. Thin silicon solar cells are distinguished from traditional silicon solar cells that are comprised of ~0.3mm thick wafers or sheets of silicon. The common defining

feature of a thin silicon solar cell is a relatively thin (<0.1mm) "active" layer or film of silicon formed on, or attached to, a passive supporting substrate.

Silicon thin-film cells are mainly deposited by chemical vapor deposition (typically plasma-enhanced, PE-CVD) from silane gas and hydrogen gas. Depending on the deposition parameters, these silicon thin films can be based on one or a combination of these materials:

- 1. Amorphous silicon (a-Si or a-Si:H) or polymorphous silicon

- 2. Microcrystalline silicon

- 3. Polycrystalline silicon (poly-Si).

These silicon thin film materials can be characterized by their grain sizes ranging from none (amorphous) to large silicon (~100 $\mu$ m) for polysilicon. The crystalline silicon TF presents dangling and twisted bonds, which results in deep defects (energy levels in the bandgap) as well as deformation of the valence and conduction bands (band tails). The solar cells made from these materials tend to have lower energy conversion efficiency than bulk silicon, but are also less expensive to produce. However, recently, solutions to overcome the limitations of thin-film crystalline silicon have been developed. Light trapping schemes where the weakly absorbed long wavelength light is obliquely coupled into the silicon and traverses the film several times can significantly enhance the absorption of sunlight in the thin silicon films. Thermal processing techniques can significantly enhance the crystal quality of the silicon and thereby lead to higher efficiencies of the final solar cells.

#### i) Amorphous Silicon (a-Si:H) Solar Cells

Amorphous silicon (a-Si:H) is the best developed thin film material and has been in commercial production since 1980.

As a material for photovoltaics, it has been the advantages of relatively cheap, using layers of a-Si:H only a few hundreds nanometers thick, low temperature (<300°C) deposition and the possibility of growing on a variety of substrates, including glass and ceramics, metals such as stainless steel, and plastics. This means that they use less than 1% of the raw material (silicon) compared standard crystalline Silicon (c-Si) cells, leading to a significant cost saving. The amorphous nature has several important consequences for photovoltaics. Absorption of visible light is better than for crystalline silicon, but doping and charge transport are more difficult that limits the conversion of sunlight quite as efficiency. The availability of alloys with different band gap enables the design of heterostructure and tandem devices.

Unlike crystal silicon, in which atomic arrangements are regular, amorphous silicon features irregular atomic arrangements. For this reason, the reciprocal action between photons and silicon atoms occurs more frequently in amorphous silicon than in crystal silicon, allowing much more light to be absorbed. As a result, instead of the indirect bandgap of crystalline Si, it basically has a direct band gap. The absorption coefficient in a-Si is, therefore, much higher than that in crystalline Si, and, therefore, a much lower thickness is required to achieve the same absorption. However, the bandgap is also larger, 1.7 to 1.9eV. Therefore, a large part of the infrared light cannot be absorbed in amorphous Si. Alloys can be deposited by adding germanium (to forma-SiGe:H) or carbon (to form a-SiC:H) precursors to the gas flow, so that the bandgap can be tuned to some extent. Finally, amorphous cells with different light absorption properties deposited continuously, one on top of another, to capture the broad solar spectrum more effectively. This increases the energy conversion efficiency of the multi-cell device and improves performance stability.

Amorphous silicon films are fabricated using plasma vapor deposition techniques to apply silane (SiH<sub>4</sub>) to the substrate or other beneficial film, allowing large-area solar cells to be fabricated much more easily than with conventional c-Si. Three amorphous silicon layers, p-layer, i-layer, and n-layer, are formed consecutively on the substrate.

The current status of a-Si:H is that: i) a-Si:H single junction p-i-n laboratory cells with highest confirmed stable efficiency of 10.1% as recently reported by Oerlikon Solar were obtained on low-cost, commercially mass-fabricated float line transparent conducting oxide (TCO) glass, ii) rapid deposition processes are being refined so that high rate, high quality can be achieved, iii) research into light degradation remedies will provide for cells with efficiencies comparable with c-Si cells, and iv) new applications for a-Si cells are being sought such as building-integrated PV, space power, consumer electronics, grid integration, and large scale power generation [9].

When silicon thin films are deposited by plasma enhanced chemical vapor deposition in a plasma regime close to powder formation, a new type of material, consisting of an amorphous matrix in which silicon nanocrystallites are embedded is obtained. This material, named hydrogenated polymorphous silicon (pm-Si:H), exhibits enhanced transport properties with respect to state-of-the-art hydrogenated amorphous silicon (a-Si:H). Hydrogenated polymorphous silicon has developed as an alternative to a-Si:H and its application to p-i-n solar cells has resulted in devices with improved stability, i.e. lower defect density and longer diffusion length. [10]. It has a lower initial and stabilized density of states, and a hole mobility considerably higher than state-of-the-art a-Si:H, which makes this material an interesting candidate for solar cell applications. Stable single-junction p-i-n solar cells based on polymorphous silicon with efficiencies close to 10% were demonstrated [11].

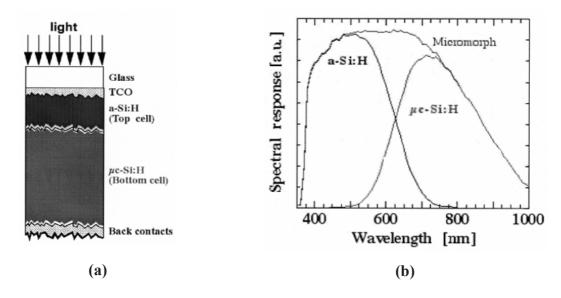

#### ii) Micromorph (a-Si/µc-Si) Silicon Solar Cells

The silicon-based tandem concept based on superposing an amorphous and a microcrystalline silicon layer is commonly called the "micromorph" concept. The details on a-Si structure and formation were discussed above. When we consider the microcrystalline silicon (µc-Si:H) as component of the micromorph concept, microcrystalline Si is grown using a strong hydrogen dilution of silane. This material has an optical absorption coefficient quite similar to that of polycrystalline silicon and its optical bandgap energy is around 1.0eV [5]. It contains both amorphous and crystalline regions [12]. The columnar grains can be several 100nm wide and several µm long. The space between these crystalline grains is filled with amorphous silicon and/or voids. The crystalline volume content of the films depends on the deposition conditions, in particular the silane concentration in the gas mix. The regime around 6% silane concentration is called the "transition region" and gives the best µc-Si:H solar cells [13].

For micromorph tandem cell concept, amorphous and microcrystalline silicon pin based cells are used in a top and a bottom photovoltaic cell as depicted in Figure 1.4a. The industrial relevance of  $\mu$ c-Si:H solar cells improves enormously if they are combined with thin a-Si:H top cells, forming a 2-cell tandem stack in which the a-Si:H cell faces the sun. This device structure has been pioneered by University of Neuchatel in the 1990s. Sharp produces cells using this system in order to more efficiently capture blue light, increasing the efficiency of the cells during the time where there is no direct sunlight falling on them. The micromorph solar cell concept is the key for achieving high efficiency stabilized thin film silicon solar cells. Micromorph tandem solar cells showed under outdoor conditions higher short-circuit currents due to the enhanced blue spectra of real sun light and therefore higher efficiencies than under AM1.5 solar simulator conditions. Furthermore, a weak air mass dependence of the short-circuit current density could be observed for such micromorph tandem solar cells. It absorbs a broader spectrum of light as shown in Figure 1.4b since current matching (between top and bottom cell) is a crucial factor in tandem cells, the efficiency measured strongly depends on having a precise incoming light spectrum.

Figure 1.4: (a) Schematic structure, and (b) corresponding spectral response of a typical micromorph tandem [13].

Tandem solar cells present an elegant way of obtaining higher efficiencies and overcoming the efficiency limits of single-junction cells. They are specially interesting for thin-film solar cells, and are presently widely used in the case of single-junction (SJ) a-Si:H solar cells. It must be notice that, the optimum top a-Si:H i-layer thickness is larger for tandem cells than for SJ cells because the slightly reduced or unaltered tandem cell current overcompensates a drop in FF.

From the practical technological point of view, a tandem cell is especially interesting, if the same deposition process and the same process temperature can be used for the bottom and for the top cell. This is the case for tandems containing amorphous silicon and amorphous silicon–germanium alloys. This is also the case for the combination of amorphous silicon and microcrystalline silicon.

From the theoretical point of view, a tandem cell is interesting if the bandgaps of the two partial cells can be properly adjusted. According to numerical calculations reported in [14] the optimal bandgap combination for a tandem cell would be  $E_{g-top}=1.73\text{eV}$  and  $E_{g-bott}=1.16\text{eV}$ . This is very near the actual bandgap combination obtained with an a-Si:H top cell and a µc-Si:H bottom cell. Therefore, provided all technological problems can be overcome, cell efficiencies significantly higher than those for single-junction µc-Si:H cells (i.e. significantly higher than 10%) should become possible for such a micromorph (µc-Si:H/ a-Si:H) tandem cell combination. Recent test results from Oerlikon Solar's pilot production line in Switzerland show that full-size Micromorph modules (1.4m<sup>2</sup>) have 151W initial power or 11% initial power conversion efficiency.

However, there are several problems for micromorph cells presently faced fall into three categories. The first one is interface and interdiffusion problems, especially with respect to the critical tunnel junction between the two partial cells. The second problem is thicknessrelated problems. Because of the light-induced degradation (Staebler–Wronski effect) prevailing in a-Si:H solar cells, the amorphous top cell has to be kept thin ( $d_{top} \le 0.3 \mu m$ ). In order to avoid long deposition times (of more than 1h), the microcrystalline bottom cell has also to be kept relatively thin ( $d_{bottom} \le 2\mu m$ ), as long as deposition rates for device-quality intrinsic  $\mu$ c-Si:H layers are not substantially over 10Å/s. Thus, the short-circuit densities obtained are rather low. The third and last one is light trapping problems. It is especially difficult to obtain effective light trapping for the *amorphous top cell*, unless an 'intermediate mirror' (e.g. an intermediate ZnO layer) between the top and the bottom cell, could be successfully used. This is one of the reasons why most of the early micromorph tandems have been top-cell limited [13].

#### iii) Polycrystalline (poly-Si) Silicon Solar Cells

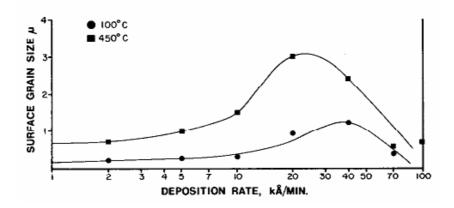

Table 1.1 depicts the grain size range depending on the type of the silicon. In this table, polysilicon is defined as having a grain size between 1µm and 1mm. In any case, this type of material has much smaller grains than standard material used for solar cells, namely multicrystalline silicon, which confusingly is still often referred to as 'polycrystalline'. The grain size is, however, much larger than for the material commonly called 'microcrystalline silicon', but also 'nanocrystalline silicon', a material typically obtained by plasma enhanced chemical vapor deposition (PECVD) at very low temperature (~200°C). This material has a typical grain size of a few tens of nanometers, still contains a substantial fraction of amorphous silicon, and in fact has the best quality in the transition region between amorphous and microcrystalline. In contrast to microcrystalline silicon, this material does not contain any amorphous tissue, or only a very small amount (well below 1%). One could think that the border between microcrystalline and polycrystalline silicon is not very sharp. In practice, there is a very clear distinction between the two materials because polysilicon is very far from the amorphous-to-crystalline transition, and always involves much higher temperatures than those used for microcrystalline silicon. Furthermore, polycrystalline silicon is composed of many silicon crystalline grains of varied crystallographic orientation.

Presently, polysilicon is commonly used for the conducting gate materials in semiconductor devices such as MOSFETS. It has also a potential for large-scale photovoltaic devices. Thin-film polysilicon solar cells have active layers that are usually thinner than 5µm,

often about only 2µm. Hence, the use of polycrystalline silicon in the production of solar cells requires less material and therefore provides for higher profits and increased manufacturing throughput. Polycrystalline silicon does not need to be deposited on a silicon wafer to form a solar cell; rather it can be deposited on other-cheaper materials, thus reducing the cost. Not requiring a silicon wafer alleviates the silicon shortages occasionally faced by the microelectronics industry [15].

| Type of Silicon          | Abbreviation | Crystal Size Range | Deposition Method                                                |

|--------------------------|--------------|--------------------|------------------------------------------------------------------|

| Single-crystal silicon   | sc-Si        | >10cm              | Czochralski,<br>Float zone                                       |

| Multicrystalline silicon | mc-Si        | 1mm – 10cm         | Cast, sheet, ribbon                                              |

| Polycrystalline silicon  | poly-Si      | 1μm – 1mm          | Chemical-vapor<br>deposition<br>(at High temperature<br>≥1000°C) |

| Microcrystalline silicon | μc-Si        | 10nm – 1µm         | Ex.: Plasma deposition                                           |

| Nanocrystalline silicon  | nc-Si        | 1 – 10nm           | (at Low temperature<br><600°C)                                   |

Table 1.1: Crystal size ranges and deposition methods depending on the crystal silicon

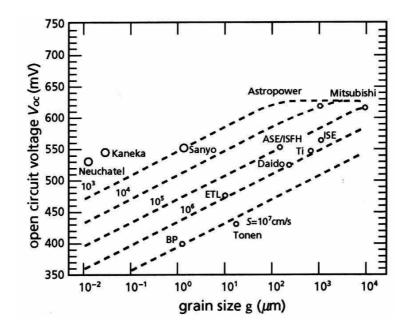

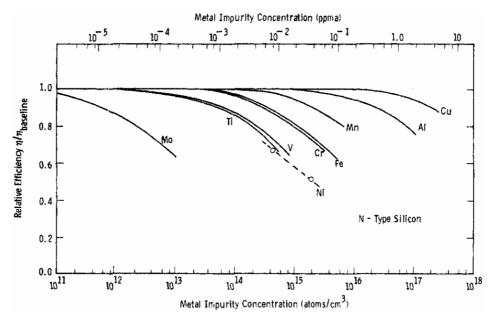

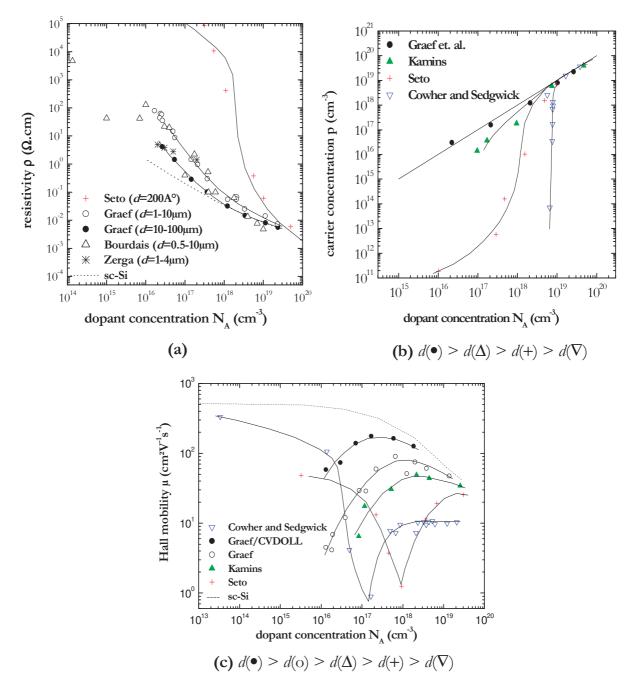

On the other hand, grain size has been shown to have an effect on the efficiency of polycrystalline silicon based solar cells. The solar cell efficiency increases with grain size. This effect is due to reduced recombination in the solar cell. Recombination, which is a limiting factor for current in a solar cell, occurs more prevalently at grain boundaries. Figure 1.5 shows the effect of grain size range on open-circuit voltage value. The larger grain size, higher  $V_{oc}$  is depicted. Additionally, thin-film solar cells of polycrystalline silicon can be manufactured with cost-beneficial deposition processes on inexpensive substrates. For instance, such solar cells can be deposited on a large-area, have a relatively high efficiency, and require less material in comparison to crystalline solar cells. As the technology does not require a thick transparent conducting oxide (TCO) layer to provide lateral conductance, it involves the least active material of all the traditional thin-films. Very effective light-trapping is the key to this minimal material use. Moreover, the key materials are silicon and its oxide and nitride rather than the complex and often metastable phases required by other thin-film technologies [16]. The other advantage is rapidly increasing performance, with small module efficiency presently in the 10–11% range, but improving steadily towards a value that appears

to lie in the 12–13% range. For instance, the best efficiency of thin film poly-Si obtained so far with this so-called CSG (Crystalline Silicon on Glass) technology is 10.4% with a 94-cm<sup>2</sup>, 20-cell mini-module. The polysilicon devices show high manufacturing yields of >90%. CSG, where the polycrystalline silicon is 1-2 $\mu$ m, is noted for its stability and durability; the use of thin film techniques also contributes to a cost savings over bulk photovoltaics. Despite the numerous advantages over alternative design, production cost estimations on a per unit area basis show that these devices are comparable in cost to single-junction amorphous thin film cells [17]. Thereof, the progress of thin film polycrystalline silicon in the last few years has been very fast. Further, polycrystalline silicon solar cells can be interconnected in integrated fashion to form modules, are environmentally safe, and have excellent long-term stability.

Figure 1.5: Grain size range dependent open circuit voltage results considering different technologies [18].

### 1.3 OBJECTIVE AND OUTLINE OF THE THESIS

The aim of this thesis is to fabricate p- and n-type polycrystalline silicon thin films by a combination of aluminium induced crystallization and epitaxy, and to study their structural, crystallographic and electrical properties in view of producing thin film silicon solar cells on foreign substrates. The manuscript is composed of four chapters:

In *Chapter 1*, we give an overview on the status of the photovoltaic industry as well as a brief description on the present materials and technologies used nowadays for the production of photovoltaic cells and modules. The advantages and particularities of the polycrystalline silicon based solar cells are closing this chapter.

*Chapter 2* presents more extensively the crystallographic and electrical properties of the polycrystalline silicon material. In particular, the effect of the grains size, as well as grains distribution, and inter and grain defects types and density on the solar cell performances are shown. We have also displayed the various techniques of direct deposition and/or crystallization of amorphous or microcrystalline silicon to make large grains polycrystalline silicon layers. The Chapter 2 ends with a detailed overview on principles of metal-induced crystallization of amorphous silicon, more particularly the aluminium-induced crystallization (AIC) which is the skeleton of this thesis.

In *Chapter 3*, we present our experimental results on the crystallization kinetics and polysilicon growth on foreign substrates by the aluminium induced crystallization of a-Si. We investigated the effect of different experimental parameters on the crystallographic properties of the grown AIC polysilicon films on alumina or glass ceramic substrates, especially the crystallographic orientation, grain size and defects in the Si layers. Additionally, the formation of n-type AIC seed layer and the electrical analysis of n-type polycrystalline silicon films as a function of the phosphorus diffusion conditions are also studied.

*Chapter 4* mainly focuses on the comprehensive results of epitaxial thickening methods on AIC seed layer and the performance of polysilicon solar cells. The limitations of cell performance in terms of dopants distribution and cell fabrication methods are discussed in this part.

In *Chapter 5*, the concluding remarks as well the prospectives of this work are presented.

#### REFERENCES

- [3] J. Poortmans, S. Reber, S. Gall, C. Zahedi and J. Alonso, In: Proc. 19th European Photovoltaic Solar Energy Conference (2004) 397.

- [4] W. Schmidt, B. Woesten, J. Kalejs, Prog. Photovolt. 10 (2002) 129.

- [5] A.G. Aberle, Thin Solid Films 517 (2009) 4706.

- [6] http://www.solarbuzz.com/news/NewsNATE50.htm

- [8] G. Beaucarne, Advances in OptoElectronics Volume 2007, Article ID 36970, 12 pages.

- [9] http://www.rci.rutgers.edu/~dbirnie/solarclass/amorphousSi.pdf

- [10] P. Roca i Cabarrocas, Th. Nguyen-Tran, Y. Djeridane, A. Abramov, E. Johnson, G. Patriarche, J. Phys. D: Appl. Phys. 40 (2007) 2258.

- [11] S. Hama, P. Roca i Cabarrocas. Sol. Energy. Mater. Sol. Cell. 69 (2001) 217.

- [12] O. Vetterl, F. Finger, R. Carius, P. Hapke, L. Houben, O. Kluth, A. Lambertz, A. Mück, B. Rech, H. Wagner, Sol. Energy. Mater. Sol. Cell. 62 (2000) 97.

<sup>[1]</sup> A. Jäger-Waldau, PV Status Report 2008, European Commission Joint Research Centre Institute for Energy, September 2008.

<sup>[2] &</sup>quot;Solar Generation V – 2008", Greenpeace and EPIA.

<sup>[7]</sup> M. Powalla, D. Bonnet, Advances in OptoElectronics, vol. 2007, 2007, Article ID 97545, 6 pages.

[13] A. Shah, J. Meier, E. Vallat-Sauvain, C. Droz, U. Kroll, N. Wyrsch, J. Guillet, U. Graf, Thin Solid Films 403-404 (2002) 179.

[14] T.J. Coutts, J.S. Ward, D.L. Young, T.A. Gessert, R. Noufi, In: Proc. 12th International Photovoltaic Science & Engineering Conf. (2001) 277.

[15] P.A. Basore, In: Proc. 21st European Photovoltaic Solar Energy Conference (2006) 544.

[16] M.A. Green, Thin-film Photovoltaics, in Advances in Solar Energy an Annual Review of Research and Development, Ed. D.Y. Goswami, Am. Sol. Energy Soc., New York, 2003.

[17] M.A. Green, Sol. Energ., 76 (2004) 3.

[18] http://www.ese.iitb.ac.in/~chetan/Lecture-34%20SPT-DEC.pdf

## **CHAPTER 2: POLYCRYSTALLINE SILICON THIN FILMS**

#### 2.1 PROPERTIES OF POLY-SI

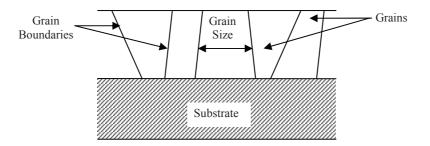

Polycrystalline silicon films are composed of independent crystalline grains which are bounded by interfaces with the substrate or with the adjacent grains named as grain boundary. A schematic view of polycrystalline silicon on a substrate is shown in Figure 2.1. Their properties and characteristics are inherently those of the grains and grain boundaries. Therefore the grain structure is of importance in the application of polycrystalline thin films.

Figure 2.1: Schematic cross section of a polycrystalline silicon thin film on a substrate.

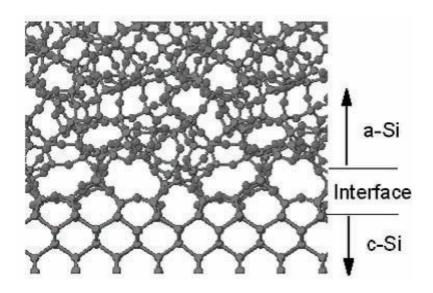

The silicon grains are arranged with random orientations to each other. The material is crystalline over the width of a grain, which is typically of the order of  $\mu$ m. Since the grains are large in terms of quantum mechanical, the band structure, and therefore the absorption coefficient, is virtually identical to that of the single crystal material. However the transport and recombination properties are strongly affected by the presence of the grain boundaries and intra-grains defects.

### 2.1.1 Crystallographic Properties of Polycrystalline Materials

A polycrystalline material is commonly formed of an aggregate of single crystal grains. The size of the grains can range from micrometres to being visible to the naked eye. Even within the single crystal grains the lattice is not perfect and can contain defects which have important effects on the mechanical and electrical behavior of the material. The microstructure of a material refers to the assemblage of grains together with other microscopic constituents such as pores and inclusions. Depending on the observe region, optical microscopy (OM), scanning electron microscopy (SEM), electron back scattering diffraction (EBSD) and transmission electron microscopy (TEM) are often used to examine the

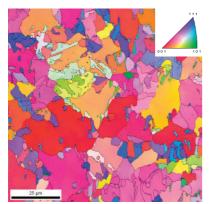

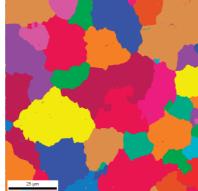

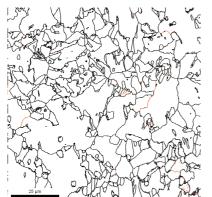

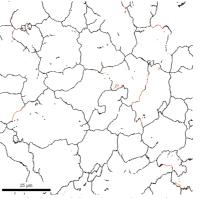

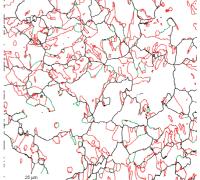

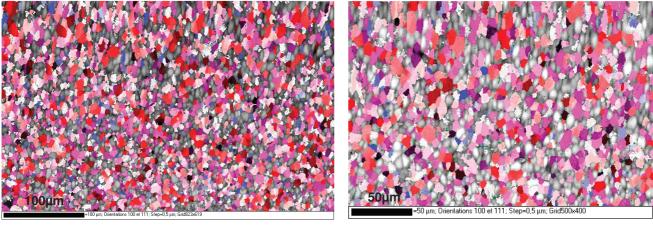

microstructures. In particular, the EBSD technique can serve as a powerful tool to extract from the same data much information such as the texture, the grain sizes, the type of grain boundaries and the density of defects. As an example, Figure 2.2 displays surface images of the same area of a polycrystalline silicon film as deduced by EBSD.

Orientation map (*including twins*)

Orientation map (*excluding twins*)

High and low angle grain boundaries map (*including twins*) [orange lines → LAGBs black lines → HAGBs]

High and low angle grain boundaries map (*excluding twins*) [orange lines → LAGBs black lines → HAGBs (without twins)]

High angle and twin boundaries map [black lines—high angle red lines  $\rightarrow \Sigma 3$  twin (60°) green lines  $\rightarrow \Sigma 9$  twin (38.9°)]

twins)]

Figure 2.2:EBSD analysis of a polycrystalline silicon.

Each image of Figure 2.2 is providing a valuable information of the observed silicon surface ranging from the crystallographic orientation of each grain composing the layer to the type and density of intra-grains defects. Before to go into details, let's recall the definition of twins in crystalline materials in general.

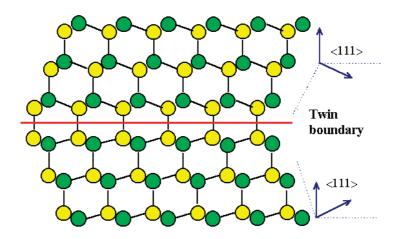

*Twinning* represents a change in the crystal orientation across a twin plane, such that a certain symmetry exists across the plane. In case of a twin boundary, the atomic arrangements on each side of it are mirror images of each other without changing any bond lengths or bond

angles as shown in Figure 2.3. The symmetry of the lattice may permit the relationship to be established by other lattice transformations as well as the reflection operation. These lattice transformations are simply ways of mathematically transforming the lattice to the twin relation. Rotation twins occur when the lower crystal can be brought into correspondence with the upper section by a  $60^{\circ}$ ,  $90^{\circ}$ , or  $180^{\circ}$  rotation. In addition to these relations there are others defined by various crystallographic operations.

Figure 2.3: A schematic diagram of twinned crystals [1].

Figure 2.2a and 2.2b exhibit the crystalline orientation map of the grains including and excluding twins, respectively. The grains in polycrystalline materials are not usually oriented randomly. The grains often cluster close to certain orientations. The way in which the orientations cluster is called the texture. The different colors of the orientation map correspond to the different crystallographic orientations of the grains. The meaning of orientation of each is given by a color chart that is the inset figure of the orientation map including twins. When excluding the twin boundaries during the data plot, the grain size drastically increases. The crystalline orientation map gives thus information about the orientation of the grains and the preferred orientation of the surface. For example, the preferred orientation of the EBSD analyzed poly-Si film sample is <100>.

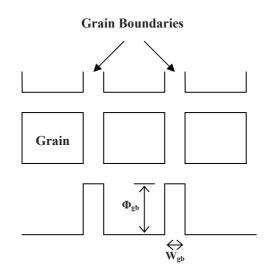

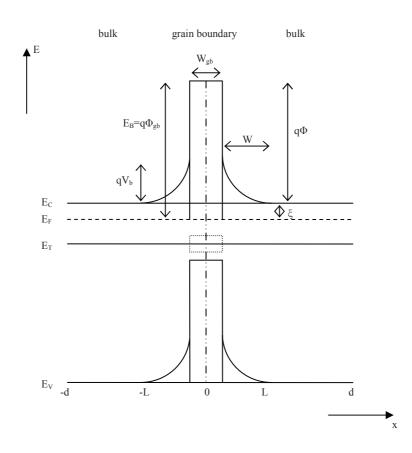

In polycrystalline materials, lattice misorientations between the adjoining, randomly oriented crystallites result in *grain boundaries* (see Figure 2.2c). A grain boundary represents a transition between crystals having no particular orientation relationship to one another. The grain boundary is considered as a two-dimensional defect, but in reality there is a specific thickness associated with this defect. In general, the grain boundaries contain high density of interface states that may trap free carriers, cause carrier scattering, and act as sink for the impurity segregation [2].

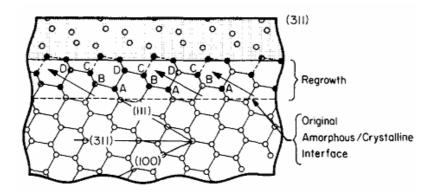

It is usually convenient to separate grain boundaries by the extent of the misorientation between the two grains:

→ The low angle grain boundaries (LAGBs) are those with a misorientation less than about 11 degrees. Generally speaking they are composed of an array of dislocations and their properties and structure are a function of the misorientation.

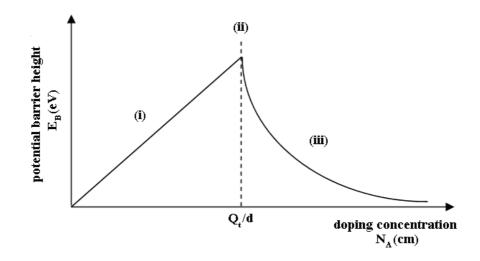

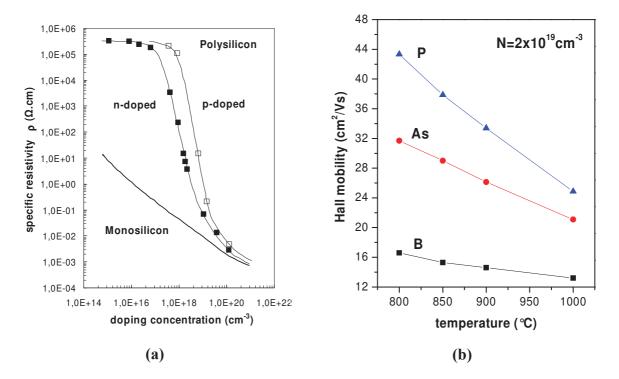

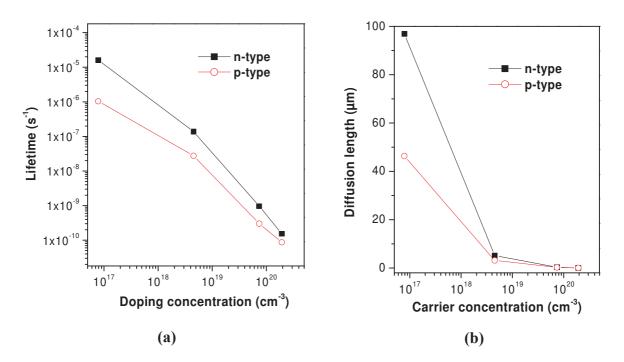

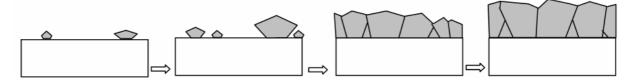

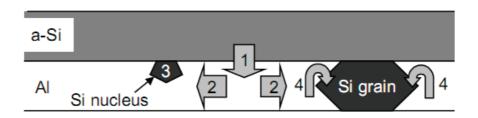

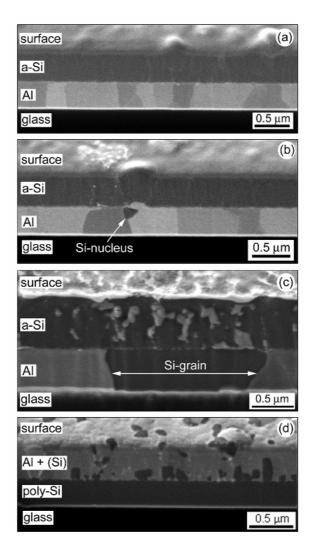

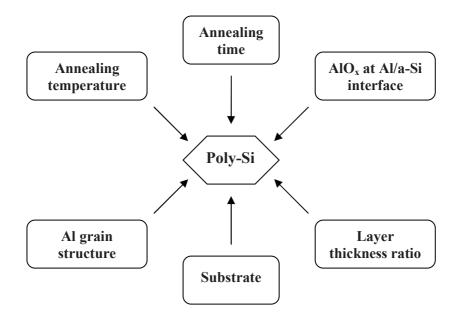

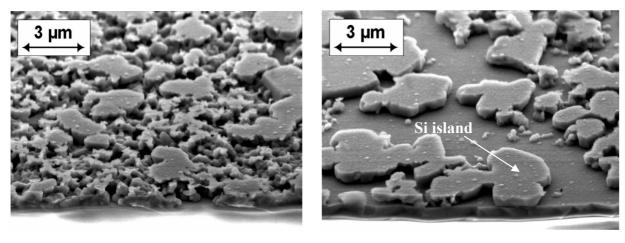

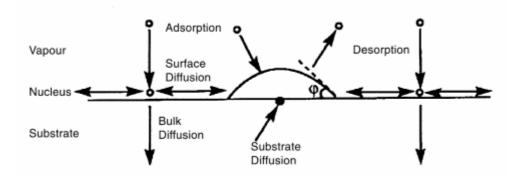

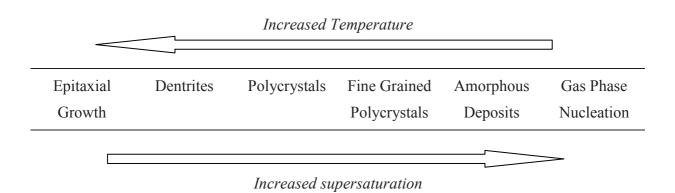

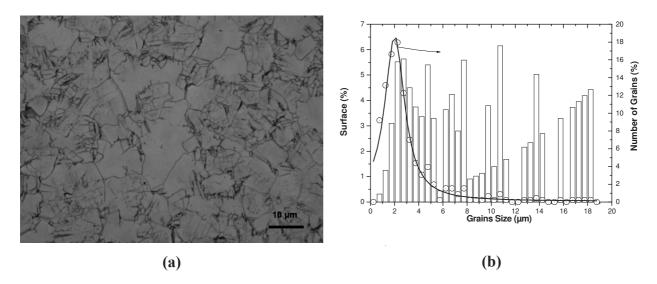

The high angle grain boundaries (HAGBs) whose misorientation is greater than about 11 degrees (the transition angle varies from 10-15 degrees depending on the material) are normally found to be independent of the misorientation. However there are "special boundaries" at particular orientations whose interfacial energies are notably lower than those of general HAGBs.