N° d'ordre:

# École Doctorale Mathématiques, Sciences de l'Information et de l'Ingénieur

#### UdS - INSA - ENGEES

## THÈSE

présentée pour obtenir le grade de

## Docteur de l'Université de Strasbourg

Discipline: Informatique

par

## Benoît Pradelle

## Static and Dynamic Methods of Polyhedral Compilation for an Efficient Execution in Multicore Environments

Méthodes Statiques et Dynamiques de Compilation Polyédrique pour l'Exécution en Environnement Multi-Cœurs

Soutenue publiquement le 20 décembre 2011

#### Membres du jury:

Directeur de thèse: Philippe Clauss, Professeur, UdS, Strasbourg

Rapporteur: Albert Cohen, Directeur de Recherche, INRIA - ENS, Paris

Rapporteur: Sanjay V. Rajopadhye, Associate Professor, CSU, Fort Collins, USA

Examinateur: William Jalby, Professeur, UVSQ - Exascale, Versailles

Examinateur: Jean Christophe Beyler, Senior Software Engineer, Intel, Versailles

«Le véritable voyage de découverte ne consiste pas à chercher de nouveaux paysages, mais à avoir de nouveaux yeux.» — Marcel Proust

## Contents

| R        | ésum | é en F  | rançais                                   | 15 |

|----------|------|---------|-------------------------------------------|----|

| 1        | Intr | oducti  | on                                        | 39 |

| <b>2</b> | Bas  | ic Con  | cepts and Related Work                    | 43 |

|          | 2.1  | Static  | Methods                                   | 44 |

|          |      | 2.1.1   | Polyhedral Parallelization                | 44 |

|          |      | 2.1.2   | Binary Code Parallelization and Rewriting | 45 |

|          | 2.2  | Static- | -Dynamic Collaborative Methods            | 46 |

|          |      | 2.2.1   | Iterative Compilation                     | 46 |

|          |      | 2.2.2   | Hybrid Code Selection                     | 47 |

|          | 2.3  | Dynan   | nic Methods                               | 48 |

|          |      | 2.3.1   | Dynamic Code Selection                    | 48 |

|          |      | 2.3.2   | The Inspector/Executor Model              | 49 |

|          |      | 2.3.3   | Thread-Level Speculation                  | 50 |

|          |      | 2.3.4   | Binary Code Parsing                       | 51 |

|          |      | 2.3.5   | Inline Code Generation and Transformation | 51 |

|          | 2.4  | The P   | olyhedral Model                           | 53 |

|          |      | 2.4.1   | Mathematical Background and Notations     | 53 |

|          |      | 2.4.2   | Scope and SCoP                            | 55 |

|          |      | 2.4.3   | Statement and Iteration Vector            | 56 |

|          |      | 2.4.4   | Iteration Domain                          | 56 |

|          |      | 2.4.5   | Access Functions                          | 57 |

|          |      | 2.4.6   | Schedule                                  | 58 |

|          |      | 2.4.7   | Data Dependence                           | 60 |

|          |      | 2.4.8   | Transformation                            | 62 |

|          |      | 2.4.9   | Code Generation                           | 65 |

|          |      | 2.4.10  | Extensions to the Polyhedral Model        | 65 |

|          |      | 2.4.11  | Tools                                     | 66 |

|          | 2.5  | Conclu  | asion                                     | 67 |

| 3        | Bin  | ary Co  | ode Parallelization                       | 69 |

|          | 3.1  | Introd  | uction                                    | 69 |

|          | 3.2  | Decom   | npiling x86-64 Executables                | 71 |

|          |      | 3.2.1   | Basic Analysis                            | 71 |

|          |      | 3.2.2   | Memory Access Description                 | 71 |

6 CONTENTS

|   |     | 3.2.3  | Induction Variable Resolution               |  | <br>• |  |         | 1/2 |

|---|-----|--------|---------------------------------------------|--|-------|--|---------|-----|

|   |     | 3.2.4  | Tracking Stack Slots                        |  |       |  |         | 73  |

|   |     | 3.2.5  | Branch Conditions and Block Constraints .   |  |       |  |         | 76  |

|   | 3.3 | Polyhe | edral Parallelization                       |  |       |  |         | 78  |

|   |     | 3.3.1  | Memory Accesses                             |  |       |  |         | 78  |

|   |     | 3.3.2  | Operations                                  |  |       |  |         | 80  |

|   |     | 3.3.3  | Scalar References                           |  |       |  |         | 82  |

|   |     | 3.3.4  | Parallelization                             |  |       |  |         | 84  |

|   |     | 3.3.5  | Reverting the Outlining                     |  |       |  |         | 84  |

|   |     | 3.3.6  | Live-in Registers                           |  |       |  |         | 85  |

|   |     | 3.3.7  | Live-out Registers                          |  |       |  |         | 86  |

|   |     | 3.3.8  | Implementation                              |  |       |  |         | 86  |

|   | 3.4 | Evalua | ation                                       |  |       |  |         | 88  |

|   |     | 3.4.1  | Loop Coverage                               |  |       |  |         | 88  |

|   |     | 3.4.2  | Binary-to-binary vs. Source-to-source       |  |       |  |         | 89  |

|   |     | 3.4.3  | Binary-to-binary vs. Hand-Parallelization . |  |       |  |         | 92  |

|   | 3.5 | Extens | sion to Complex Codes                       |  |       |  |         | 94  |

|   |     | 3.5.1  | Extension to Parametric Codes               |  |       |  |         | 94  |

|   |     | 3.5.2  | Extension to Polynomial Codes               |  |       |  |         | 96  |

|   |     | 3.5.3  | In-Place Parallelization                    |  |       |  |         | 96  |

|   | 3.6 | Relate | ed Work                                     |  |       |  | <br>. 1 | :03 |

|   |     | 3.6.1  | Decompilation and Address Expressions       |  |       |  | <br>. 1 | 03  |

|   |     | 3.6.2  | Parallelization and Transformation Strategy |  |       |  | <br>. 1 | .04 |

|   | 3.7 | Concl  | usion and Perspectives                      |  |       |  | <br>. 1 | 04  |

|   | ~   |        |                                             |  |       |  |         |     |

| 4 |     |        | sion Selection                              |  |       |  |         | 07  |

|   | 4.1 |        | uction                                      |  |       |  |         | .07 |

|   | 4.2 |        | ion Framework Overview                      |  |       |  |         | 30. |

|   | 4.3 |        | ating Different Code Versions               |  |       |  |         |     |

|   | 4.4 |        | ng the Code Versions                        |  |       |  |         |     |

|   |     |        | Strategy 1                                  |  |       |  |         |     |

|   |     | 4.4.2  | Strategy 2                                  |  |       |  |         | 16  |

|   |     | 4.4.3  | Parametric Ranking Table                    |  |       |  |         | 22  |

|   | 4.5 |        | me Selection                                |  |       |  |         | 24  |

|   |     | 4.5.1  | Iteration Count Measurement                 |  |       |  |         | 24  |

|   |     | 4.5.2  | Load Balance                                |  |       |  |         | 25  |

|   |     | 4.5.3  | Predicting the Execution Time               |  |       |  |         | .26 |

|   |     | 4.5.4  | Discussion                                  |  |       |  |         | 26  |

|   | 4.6 | -      | iments                                      |  |       |  |         | 27  |

|   |     | 4.6.1  | Dynamic Scheduling of Regular Codes         |  |       |  |         | 30  |

|   |     | 4.6.2  | Execution Context Characteristics           |  |       |  |         | 32  |

|   |     | 4.6.3  | Execution Time Gains                        |  |       |  |         | 34  |

|   |     | 161    | Accuracy                                    |  |       |  | 1       | 34  |

|   | 4.7 | 4.6.4  | usion and Perspectives                      |  |       |  |         | 37  |

CONTENTS 7

| 5  | Spec  | culativ | ve Parallelization                | 139 |

|----|-------|---------|-----------------------------------|-----|

|    | 5.1   | Introd  | uction                            | 139 |

|    | 5.2   | Overvi  | iew                               | 140 |

|    |       | 5.2.1   | Speculations                      | 140 |

|    |       | 5.2.2   | General overview                  | 142 |

|    |       | 5.2.3   | Evaluation Environment            | 143 |

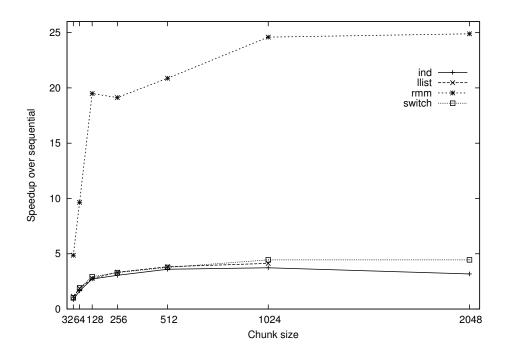

|    |       | 5.2.4   | Chunking                          | 144 |

|    | 5.3   | Online  | Profiling                         | 146 |

|    |       | 5.3.1   | Inspector Profiling               | 146 |

|    |       | 5.3.2   | Profiling on a Sample             | 147 |

|    |       | 5.3.3   | Chosen Solution                   | 147 |

|    | 5.4   | Depen   | dence Construction                | 148 |

|    | 5.5   | Schedi  | ıling                             | 148 |

|    |       | 5.5.1   | PLUTO                             | 148 |

|    |       | 5.5.2   | Offline Profiling and Scheduling  | 149 |

|    |       | 5.5.3   | Generic Schedules                 | 150 |

|    |       | 5.5.4   | Dependence Testing                | 151 |

|    |       | 5.5.5   | Chosen Solution                   | 152 |

|    | 5.6   | Code    | Generation                        | 153 |

|    |       | 5.6.1   | Runtime Compilation               | 153 |

|    |       | 5.6.2   | Hybrid Code Generation            | 155 |

|    |       | 5.6.3   | Static Code Generation            | 156 |

|    |       | 5.6.4   | Chosen Solution                   | 157 |

|    | 5.7   | Specul  | lation Verification               | 157 |

|    |       | 5.7.1   | Parallel Speculation Verification | 158 |

|    |       | 5.7.2   | Verification Implementation       | 159 |

|    |       | 5.7.3   | Test Implementation               | 161 |

|    |       | 5.7.4   | Chosen Solution                   | 161 |

|    | 5.8   | Comm    | it and Rollback                   | 161 |

|    |       | 5.8.1   | Transactions and Chunks           | 162 |

|    |       | 5.8.2   | fork-based Transactional System   | 163 |

|    |       | 5.8.3   | memcpy-based Transactional System | 165 |

|    |       | 5.8.4   | Interrupting the Threads          | 165 |

|    |       | 5.8.5   | Rollback Strategies               | 166 |

|    |       | 5.8.6   | Chosen Solution                   | 167 |

|    | 5.9   | Puttin  | g it all Together                 | 168 |

|    |       | 5.9.1   | Overview                          | 168 |

|    |       | 5.9.2   | Evaluation                        | 169 |

|    | 5.10  | Conclu  | usion and Perspectives            | 170 |

| 6  | Con   |         | n and Perspectives                | 171 |

|    | 6.1   |         | butions                           | 171 |

|    | 6.2   | Future  | e work                            | 173 |

| Bi | bliog | raphy   |                                   | 178 |

8 CONTENTS

## List of Figures

| 1      | Aperçu du système de parallélisation. (1) Les nids de boucles analysables sont convertis en programmes C contenant seulement les accès mémoires |          |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|        | et le code de contrôle. (2) Cette représentation intermédiaire est envoyée                                                                      |          |

|        | à un paralléliseur source-à-source. (3) Le programme parallèle résultant                                                                        |          |

|        | est complété avec les calculs sur les données puis recompilé avec un                                                                            |          |

|        | compilateur C classique.                                                                                                                        | 16       |

| 2 3    |                                                                                                                                                 | 19       |

| 0      | 2) le code source extrait du programme binaire                                                                                                  | 20       |

| 4      | Comparaison de notre système à une parallélisation manuelle et à l'état                                                                         | 20       |

| 4      | de l'art.                                                                                                                                       | 21       |

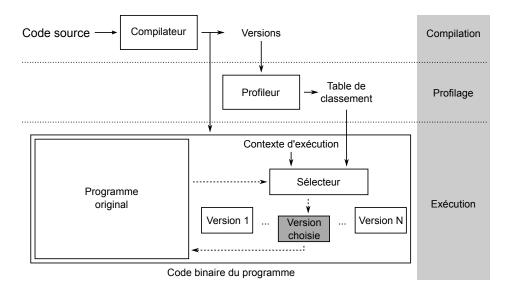

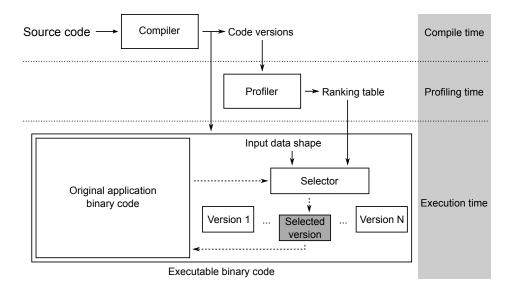

| E      | Schéma général du sélecteur de versions                                                                                                         | 23       |

| 5<br>6 | Temps d'exécution (en secondes) réel et prédit de toutes les versions                                                                           | 20       |

| U      | du programme 2mm dans tous les contextes testés, trié par le temps                                                                              |          |

|        | d'exécution réel. Sur Core i7 avec la stratégie 1                                                                                               | 28       |

| 7      | <u> </u>                                                                                                                                        | 2C       |

| 1      | Temps d'exécution (en secondes) réel et prédit de toutes les versions                                                                           |          |

|        | du programme 2mm dans tous les contextes testés, trié par le temps                                                                              | 20       |

| 0      | d'exécution réel. Sur Core i7 avec la stratégie 1                                                                                               | 28       |

| 8      | Les différentes étapes de notre paralléliseur spéculatif                                                                                        | 29<br>32 |

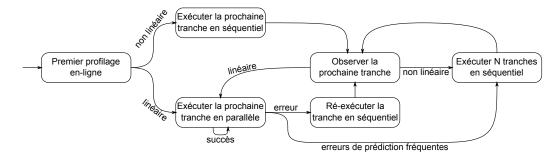

| 9      |                                                                                                                                                 |          |

| 10     | Stratégie de ré-exécution spéculative                                                                                                           | 33       |

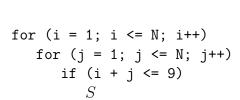

| 2.1    | Sample loop nest (left) and the iteration domain of $S$ (right)                                                                                 | 56       |

| 2.2    | Sample loop nest with two statements                                                                                                            | 59       |

| 2.3    | A matrix-vector product                                                                                                                         | 62       |

|        | •                                                                                                                                               |          |

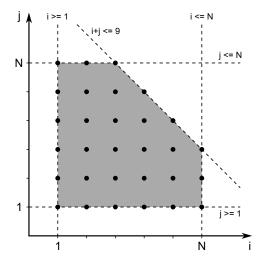

| 3.1    | Overview of the parallelization system. (1) Analyzable portions of the sequential binary program are raised to simple C loop nests only con-    |          |

|        | taining the correct memory accesses, and (2) sent to a back-end source-                                                                         |          |

|        | to-source parallelizer. (3) The resulting parallel loop nest is filled with                                                                     |          |

|        | actual computations, and compiled using a standard compiler                                                                                     | 70       |

| 3.2    | Symbolic address expressions in a loop nest of depth two in binary code in                                                                      | • •      |

| J      | SSA form: (a) after recursive register substitution, and (b) after induction                                                                    |          |

|        | variable resolution. Indentation is used to highlight the loop levels. "@"                                                                      |          |

|        | denotes address expressions                                                                                                                     | 74       |

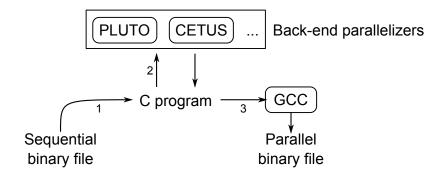

| 3.3    | Sample CFG (left), its corresponding reversed CFG (center), and post-                                                                           |          |

| 3.0    | dominator tree (right)                                                                                                                          | 77       |

10 LIST OF FIGURES

| 3.4  | Sample code parallelization using PLUTO                                                           | 76       |

|------|---------------------------------------------------------------------------------------------------|----------|

| 3.5  | Matrix multiply as it is extracted from the binary code                                           | 81       |

| 3.6  | Matrix multiply after simplifying the memory accesses                                             | 81       |

| 3.7  | Matrix multiply after forward substitution                                                        | 82       |

| 3.8  | Matrix multiply after scalar to array conversion                                                  | 83       |

| 3.9  | Matrix multiply after transformation by PLUTO and semantics restora-                              |          |

|      | tion                                                                                              | 85       |

| 3.10 | General scheme of the implementation                                                              | 87       |

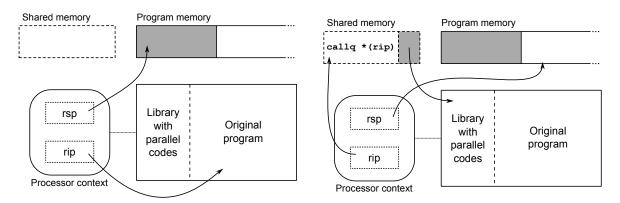

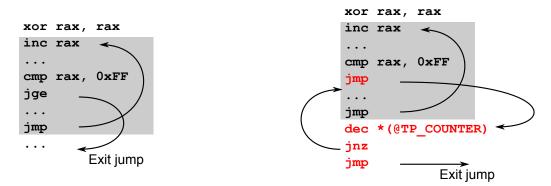

|      | Redirecting the execution flow to the parallel loop nests (left to right).                        | 87       |

|      | Parallelization back-ends applied to 1) the original source code, and to                          | •        |

| 0.12 | 2) the binary code (kernel only)                                                                  | 91       |

| 3 13 | Speedup comparison for three parallelization strategies. (initialization                          | 01       |

| 0.10 | + kernel)                                                                                         | 93       |

| 2 1/ | Original code                                                                                     | 95       |

|      | Code as seen by the dependence analyzer                                                           | 95       |

|      | Corresponding runtime tests                                                                       | 95<br>95 |

|      | Execution times (and speedups) for swim on the train dataset                                      | 96       |

|      | •                                                                                                 |          |

|      | Execution times (and speedups) for mgrid on the train dataset                                     | 98       |

| 3.19 | Overwriting loop bounds with a new loop counter (left to right)                                   | 100      |

| 4.1  | Framework overview                                                                                | 109      |

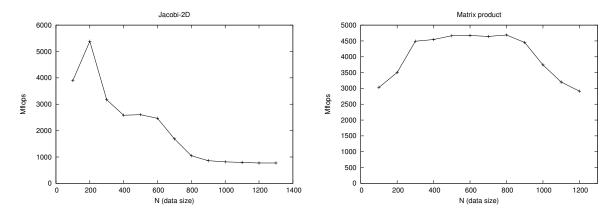

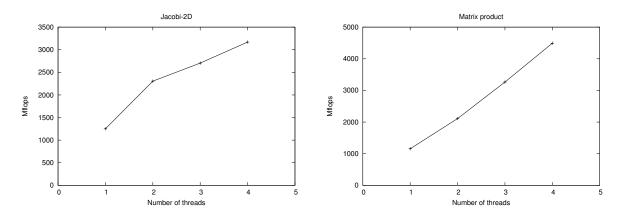

| 4.2  | Throughput of a simple parallel code for different data sizes                                     | 111      |

| 4.3  | Throughput of several versions for different data sizes                                           | 111      |

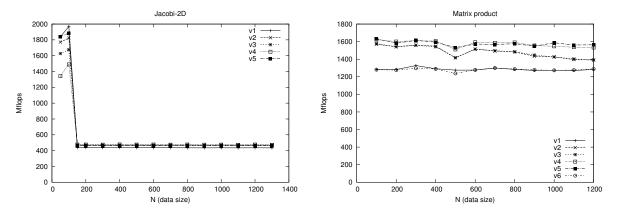

| 4.4  | Throughput of the parallelized kernels for different number of threads                            |          |

| 1.1  | used                                                                                              | 112      |

| 4.5  | Code pattern. The profiling code is generated from this code pattern                              | 112      |

| 1.0  | after some syntactic replacements                                                                 | 115      |

| 4.6  | Sample code                                                                                       | 115      |

| 4.7  | Sample profiling code for the loop nest presented in Figure 4.6                                   | 116      |

| 4.8  | Sample parameterized loop nest. Increasing M does not increase the                                | 11(      |

| 1.0  | number of iterations                                                                              | 117      |

| 4.9  | Sample loop nest and its associated iteration domain. A square of $5 \times 5$                    | 111      |

| 4.5  | iterations can fit in it, so we can guarantee that each loop level executes                       |          |

|      | at least 5 consecutive iterations                                                                 | 117      |

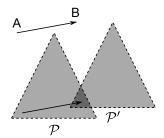

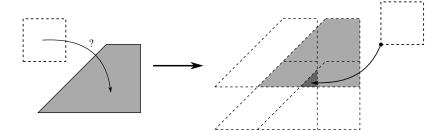

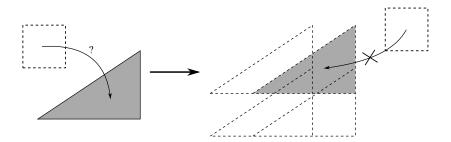

| 4.10 | The intersection of $\mathcal{P}$ and $\mathcal{P}'$ defines all the points such that $B$ can fit | 111      |

| 4.10 | in $\mathcal{P}$ , if $A$ is in $\mathcal{P}$                                                     | 118      |

| 111  | Intersection of the translated polyhedron copies in 2D space. The inter-                          | 110      |

| 4.11 | - v                                                                                               | 110      |

| 1 10 | section is not empty, the polyhedron can enclose the square                                       | 119      |

| 4.12 | Intersection of the translated polyhedron copies in 2D space. The inter-                          | 110      |

| 1 19 | section is empty: the square cannot be contained in the polyhedron                                | 119      |

|      | Profiling code pattern for strategy 2                                                             | 121      |

|      | Code sample to profile                                                                            | 121      |

|      | Profiling code generated from the code in Figure 4.14                                             | 123      |

|      | A loop nest (left) and its corresponding prediction nest (right)                                  | 125      |

| 4.17 | Loop nest and the corresponding iteration domain where the iterations                             | 10-      |

|      | are grouped by thread                                                                             | 125      |

LIST OF FIGURES 11

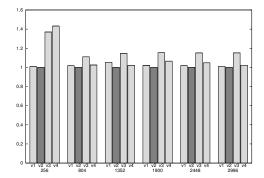

| <ul> <li>4.19 Speedup of Cilk over OpenMP static on Core i7</li> <li>4.20 Speedup of OpenMP dynamic over static on Opteron</li> <li>4.21 Speedup of Cilk over OpenMP static on Opteron</li> <li>4.22 Speedup of OpenMP dynamic over static on Phenom II</li> </ul> | 13<br>13<br>13 |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---|

| 4.21 Speedup of Cilk over OpenMP static on Opteron                                                                                                                                                                                                                 | 13<br>13       | 1 |

|                                                                                                                                                                                                                                                                    | 13             |   |

| 4.22 Speedup of OpenMP dynamic over static on Phenom II                                                                                                                                                                                                            |                | 1 |

| or truep or opening dynamic over booking our monomiti                                                                                                                                                                                                              | 19             | 1 |

| 4.23 Speedup of Cilk over OpenMP static on Phenom II                                                                                                                                                                                                               | 13             | 1 |

| 4.24 Execution times for adi on Opteron (5 threads). Version 2 is the                                                                                                                                                                                              | he best        |   |

| one for the fifth dataset                                                                                                                                                                                                                                          | 13             | 2 |

| 4.25 Execution times for adi on Core i7 (5 threads). Version 2 is the                                                                                                                                                                                              | e worst        |   |

| one for the fifth dataset                                                                                                                                                                                                                                          |                | 2 |

| 4.26 Execution times for genver on Core i7 (1 thread). Version 1 is t                                                                                                                                                                                              | the best       |   |

| one for the first dataset                                                                                                                                                                                                                                          |                | 3 |

| 4.27 Execution times for genver on Core i7 (8 threads). Version 1                                                                                                                                                                                                  |                |   |

| worst one for the first dataset                                                                                                                                                                                                                                    |                | 3 |

| 4.28 Execution times for mgrid on Phenom (4 threads). Version 4 is t                                                                                                                                                                                               |                |   |

| one for the last dataset, but is inefficient for the third dataset.                                                                                                                                                                                                |                | 3 |

| 4.29 Execution time of every version of 2mm in every execution context                                                                                                                                                                                             |                |   |

| by actual execution time on Core i7 with strategy 1                                                                                                                                                                                                                |                | 6 |

| 4.30 Execution time of every version of 2mm in every execution context                                                                                                                                                                                             |                |   |

| by actual execution time on Core i7 with strategy 2                                                                                                                                                                                                                |                | 6 |

| 4.31 Execution time of every version of jacobi-2d in every execution of                                                                                                                                                                                            |                |   |

| sorted by actual execution time on Opteron with strategy 1.                                                                                                                                                                                                        |                | 6 |

| 4.32 Execution time of every version of jacobi-2d in every execution of                                                                                                                                                                                            |                | _ |

| sorted by actual execution time on Opteron with strategy 2.                                                                                                                                                                                                        |                | 6 |

| 4.33 Execution time of every version of gemver in every execution of                                                                                                                                                                                               |                | _ |

| sorted by actual execution time on Phenom II with strategy 1.                                                                                                                                                                                                      |                | 1 |

| 4.34 Execution time of every version of gemver in every execution of                                                                                                                                                                                               |                | _ |

| sorted by actual execution time on Phenom II with strategy 2.                                                                                                                                                                                                      | 13             | 1 |

| 5.1 Main phases of the speculative system                                                                                                                                                                                                                          | 14             | 2 |

| 5.2 Sample loop nest (left) and its chunked counterpart (right)                                                                                                                                                                                                    |                |   |

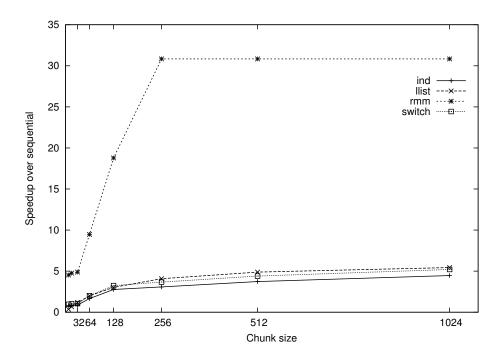

| 5.3 Speedup of each code over its sequential version, for different chr                                                                                                                                                                                            |                |   |

| 5.4 Compared compilation and execution times using GCC and LLC                                                                                                                                                                                                     |                |   |

| O1 and O3 optimization levels                                                                                                                                                                                                                                      |                | 4 |

| 5.5 Sample code (left) and its speculative parallel counterpart (right                                                                                                                                                                                             |                | 0 |

| 5.6 Sample loop (top), its transformed counterpart (bottom), and t                                                                                                                                                                                                 | *              |   |

| responding memory accesses performed (right)                                                                                                                                                                                                                       |                | 2 |

| 5.7 Execution of chunk i+1 cancelled (left) or committed (right)                                                                                                                                                                                                   | 16             | 3 |

| 5.8 Speedup over the sequential version when using a fork-based t                                                                                                                                                                                                  |                |   |

| tional system                                                                                                                                                                                                                                                      | 16             | 4 |

| 5.9 Speedup over the sequential version when using a memcpy-based                                                                                                                                                                                                  | d trans-       |   |

| actional system                                                                                                                                                                                                                                                    | 16             | 6 |

| 5.10 Runtime strategy                                                                                                                                                                                                                                              | 16             | 7 |

12 LIST OF FIGURES

## Remerciements

Je profite de ces quelques lignes de liberté pour remercier les personnes qui ont influencé ces travaux. Tout d'abord, merci à Philippe pour m'avoir soutenu et aidé durant toutes ces années. Encadrer une thèse n'est pas un vain mot pour toi et j'ai beaucoup appris à tes côtés. J'emporterai avec moi l'idée que l'innovation a besoin d'une touche de folie pour se révéler.

Merci à Alain et Vincent avec qui j'ai eu le très grand plaisir de travailler. Votre expérience et votre culture m'ont été d'une très grande aide au travers de vos conseils avisés. La plupart des travaux présentés dans cette thèse n'auraient pas été possibles sans vous. Merci à Alexandre, Alexandra, et Olivier qui m'ont supporté dans notre bureau. Merci à Stéphane, Julien, Romaric, Éric, Matthieu, Jean-François, et Étienne avec qui il est toujours très agréable de partager la journée. D'une façon générale, un grand merci à toute l'équipe ICPS pour l'ambiance formidable que chaque membre s'attache à faire régner. Merci également aux anciens de l'ICPS, en particulier à Jean-Christophe qui m'a ouvert la porte de l'équipe, et à Benoît «Homie» qui m'a initié aux secrets du modèle polyédrique. New York m'accompagne désormais.

Je remercie également tous mes amis strasbourgeois. Avec vous, j'ai toujours eu (y compris pendant la thèse) un endroit où trouver de la bonne humeur, de la chaleur, et des bons moments. Merci plus particulièrement à Emil pour toutes nos discussions passionnées et passionnantes qui m'aident à prendre du recul.

Je remercie ma famille qui m'a toujours soutenu et qui m'a laissé libre de trouver ma voie. Le calme et l'apaisement que je trouve à vos côtés me sont d'une grande aide.

Enfin, merci à toi, Annick, pour ton soutien sans faille et ta patience infinie durant toute cette thèse. Du haut de ton innocence, tu colores notre monde et, sans toi, tout cela n'aurait pas la même saveur.

14 REMERCIEMENTS

## Résumé en Français

## Introduction

Jusqu'au début des années 2000, le développement logiciel était dans une situation très favorable. En effet, les fabricants de matériel augmentaient rapidement la fréquence des processeurs à chaque nouvelle génération. Si un programme était trop lent, il suffisait simplement d'attendre la prochaine génération de processeurs pour qu'il s'exécute plus rapidement. Dans un tel contexte, le rôle d'un compilateur se borne principalement à transcrire un programme écrit dans un langage de programmation haut-niveau vers une suite d'instructions pour le processeur. Les optimisations appliquées sur le programme ne sont généralement pas vitales.

Cependant, certaines limites physiques ont été atteintes et il n'est plus possible d'augmenter encore la fréquence des processeurs. Les fabricants ont alors décidé d'augmenter le nombre de cœurs de calcul par puce afin de continuer à augmenter la puissance théorique des processeurs. Ce changement d'approche impacte fortement le développement logiciel. Pour profiter des améliorations du matériel, les logiciels doivent désormais être ré-écrits dans une version parallèle.

Cependant, les développeurs sont en général très peu sensibilisés à la programmation parallèle et préfèrent souvent ne pas la pratiquer. Étant donné que le rôle d'un compilateur est d'adapter un programme pour qu'il puisse s'exécuter efficacement sur l'ordinateur ciblé, il est raisonnable de considérer que c'est en réalité au compilateur de réaliser cette parallélisation si le programmeur ne le fait pas.

C'est ce qui a motivé toutes les approches à la parallélisation automatique proposées jusque là. L'inconvénient de ces approches automatiques est qu'elles ne sont pas vraiment prêtes pour une utilisation à grande échelle. D'immenses progrès ont été réalisés dans le domaine mais les techniques existantes ne sont pas encore assez robustes. L'urgence provoquée par l'arrivée massive de matériel multi-cœur nous pousse à développer davantage ces techniques. Nous proposons ainsi d'étendre la parallélisation automatique dans trois directions principales.

Nous proposons tout d'abord un système permettant de paralléliser les programmes qui sont exprimés sous leur forme a priori finale : le code binaire. Ensuite, nous proposons un mécanisme à l'exécution qui permet de sélectionner une implémentation efficace d'un programme parallèle parmi plusieurs afin de bénéficier au mieux des spécificités du contexte dans lequel ce programme s'exécute. Enfin nous proposons une solution de parallélisation spéculative utilisant le modèle polyédrique afin de transformer et paralléliser efficacement les programmes même lorsque leur structure est complexe et empêche la parallélisation à la compilation.

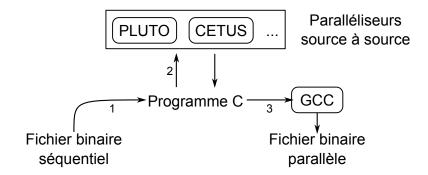

Figure 1: Aperçu du système de parallélisation. (1) Les nids de boucles analysables sont convertis en programmes C contenant seulement les accès mémoires et le code de contrôle. (2) Cette représentation intermédiaire est envoyée à un paralléliseur source-à-source. (3) Le programme parallèle résultant est complété avec les calculs sur les données puis recompilé avec un compilateur C classique.

Ces trois approches forment une réponse cohérente au problème de la parallélisation automatique des programmes. Elles utilisent tous les moments de la vie d'un programme depuis sa compilation jusqu'à son exécution afin d'exploiter autant que possible les opportunités de parallélisation. Enfin ces trois approches utilisent le modèle polyédrique dans des contextes nouveaux, permettant d'étendre son utilisation vers le code binaire, les contextes d'exécutions changeant, et les programmes dont la structure est difficilement analysable à la compilation.

## Parallélisation de Code Binaire

#### Introduction

Alors que les outils de parallélisation automatique exploitent généralement le code source des programmes, il peut être intéressant de pouvoir paralléliser des programmes compilés. Cette approche permet la parallélisation d'applications dont le code source est inaccessible au moment de la compilation. Par exemple des programmes anciens dont le code source est perdu, des applications commerciales dont le code source est tenu secret, ou des librairies utilisées par un programme, peuvent ainsi être parallélisés. Ainsi, les programmes peuvent être parallélisés au moment de leur déploiement sur différentes machines d'exécution. De cette manière, les développeurs peuvent continuer à développer et compiler normalement leurs programmes séquentiels qui seront parallélisés lors de leur installation, par le système d'exploitation par exemple.

Nous proposons un système de parallélisation de code binaire à trois étapes. La première étape consiste à décompiler le programme binaire pour en extraire une représentation intermédiaire de ses nids de boucles affines. Cette représentation intermédiaire doit être suffisamment précise pour permettre leur parallélisation. Lorsque cette parallélisation à été réalisée, le programme est alors recompilé en un programme binaire parallèle. Un aperçu de notre système est présenté en Figure 1. Comme illustré dans la figure, notre système utilise un paralléliseur source-à-source pour réaliser la paral-

lélisation des nids de boucles. Cette capacité lui permet par exemple d'appliquer des transformations polyédriques sur les programmes binaires.

### Décompilation et Analyse

La première tâche réalisée par notre système de parallélisation de code binaire est la décompilation. L'objectif de cette étape est d'analyser le programme binaire afin d'extraire une représentation intermédiaire suffisamment précise pour permettre la parallélisation des nids de boucles par un outil source-à-source. La parallélisation automatique est possible lorsque les structures de contrôle du programme ainsi que les accès mémoires sont exprimés dans une représentation facilement exploitable. Ce sont donc les deux informations que l'analyse extrait du programme compilé.

#### Analyse de base

Pour analyser le programme, nous utilisons principalement des techniques classiques d'analyse de programmes, combinés avec les résultats récents de Ketterlin et Clauss [67]. Le programme binaire est décompilé vers une suite d'instructions assembleur. Depuis cette représentation, les limites des blocs de base sont déterminées, et un graphe de flot de contrôle est calculé par routine. L'arbre des dominateurs est calculé et les boucles sont déterminées. Si une routine contient des boucles irréductibles, elle est ignorée. Le programme est ensuite mis sous forme SSA (Static Single Assignment). Les registres processeurs sont alors des variables et la mémoire est une variable unique M.

#### Substitution récursive

Dans le code binaire pour les architectures x86-64, les adresses accédées sont sous la forme  $Base + s \times Index + o$ , où Base et Index sont des registres et s et o sont des petites constantes. Cette représentation ne permet par directement une analyse de dépendances précise. Afin de simplifier ces adresses, les registres Base et Index sont récursivement remplacés par leurs définitions. Lors de ce remplacement, des  $\phi$ -fonctions peuvent être rencontrées. Une résolution de variables d'induction permet alors de construire des expressions dépendant d'indices virtuels de boucles. Lorsqu'une zone mémoire est rencontrée lors de la substitution récursive, une analyse de dépendance simple est réalisée en distinguant les accès à la pile des autres accès. Cela permet de poursuivre le remplacement lorsqu'une valeur temporaire est placée dans la pile de la fonction.

#### Résultat

À la fin de l'analyse, les adresses accédées sont exprimées, lorsque c'est possible, sous forme de fonctions linéaires dépendant d'indices virtuels de boucle ainsi que d'autres registres définis hors de la boucle. Des conditions d'exécutions des blocs de base sont également déterminées afin d'en déduire les conditions de sortie des boucles. Toutes ces informations rassemblées permettent de construire un programme C simpliste dans

lequel le flot de contrôle ainsi que les accès à la mémoire sont équivalents à ceux présents dans le code binaire original.

### Parallélisation Polyédrique

Le résultat de l'analyse génère un programme C simple qui permet la parallélisation du programme. Cependant, en l'état, ce programme simple pose plusieurs problèmes aux paralléliseurs source-à-source existant. Avant d'être parallélisé, le code source reconstruit depuis le programme binaire est donc simplifié.

#### De la mémoire aux tableaux

Les accès mémoires, même après la substitution récursive, sont sous une forme complexe dans le fichier binaire : les accès tableaux du code source original du programme sont linéarisés et les adresses de base des tableaux statiques sont de très grandes valeurs. C'est pourquoi, lorsque les bornes des boucles sont non paramétriques, nous proposons de reconstituer les dimensions des tableaux. Pour ce faire, la mémoire est séparée en zones disjointes et les dimensions des tableaux sont reconstruites par un algorithme simple évaluant toutes les dimensions possibles. Ces simplifications permettent une analyse de dépendance plus précise.

#### Les scalaires

Les écritures dans des scalaires provoquent de nombreuses dépendances qui ne sont généralement pas traitées dans les paralléliseurs source-à-source existant, en particulier les outils polyédriques. Des techniques classiques telles que la résolution de variables d'induction ainsi que l'analyse de «Forward Substitution» permettent d'éliminer certaines références à des scalaires. En plus de ces techniques, nous remplaçons, lorsque c'est possible, les références à des scalaires par des références à des tableaux existants qui génèrent généralement moins de dépendances. Cette technique peut être vue comme une expansion des scalaires suivi d'un renommage du tableau résultant de l'expansion en un autre tableau déjà présent dans le code source.

#### Parallélisation

Après simplification, le code à paralléliser contient des boucles et des tests ainsi que des accès mémoires. Les opérations réalisées sur les données, inutiles pour l'analyse de dépendances, sont remplacées par un opérateur générique tel que «+». Ce code simplifié est facilement analysable par les outils existants et peut donc être parallélisé. Dans notre implémentation, deux paralléliseurs automatiques source-à-source sont utilisés : CETUS [6], un paralléliseur relativement simple, et PLUTO [23], un paralléliseur polyédrique. Ces deux outils produisent en sortie un code C parallélisé avec OpenMP [95].

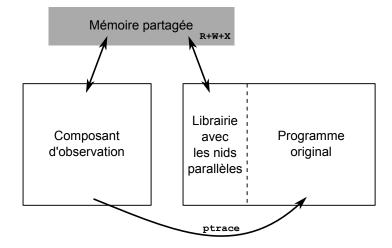

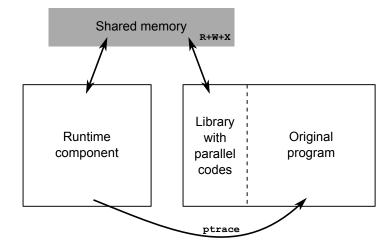

Figure 2: Implémentation du mécanisme de parallélisation de programmes binaires.

#### Restauration de la sémantique

Après la parallélisation du programme, les opérations sur les données sont ré-introduites dans le code source du programme. Ces opérations sont réalisées par des instructions assembleurs insérées dans le programme C parallélisé. Les registres SSA deviennent cependant des variables C classiques.

Le résultat est donc un ensemble de nids de boucles parallèles exprimés en langage C, et faisant référence à des variables dont le contenu est exploité par des opérations en assembleur. Ces nids sont finalement compilés par un compilateur classique pour produire la version parallèle du programme binaire initial.

#### Implémentation

La Figure 2 présente un schéma général du mécanisme permettant l'exécution des versions parallèles des nids de boucles. Les boucles parallélisées sont compilées dans une librairie dynamique, chargée dans l'espace mémoire du programme séquentiel. Au démarrage de l'application, un composant d'observation place des points d'arrêt au début de chaque boucle parallélisée dans le programme séquentiel. Lorsque ces points d'arrêts sont rencontrés, le composant d'observation reprend le contrôle et redirige l'exécution du programme vers la version parallèle du nid de boucle. Cette opération s'appuie sur une zone de mémoire partagée dans laquelle la librairie aura déclaré la position en mémoire des nids parallèles.

#### Évaluation

#### Sensibilité à l'entrée

Les optimisations appliquées lors de la compilation du programme séquentiel original ont un impact sur le nombre de boucles que notre système peut paralléliser. Afin de mieux évaluer cet impact, nous avons compilé les programmes de la suite de test PolyBench [101] avec ICC 12.1, GCC 4.5, et LLVM 2.8 en utilisant les niveaux

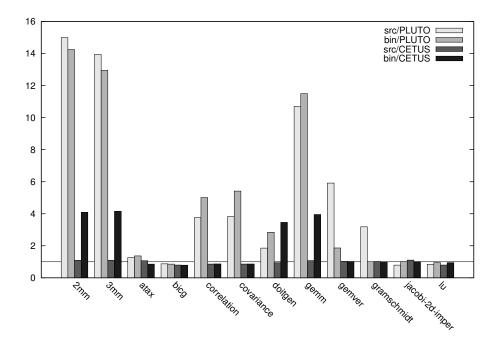

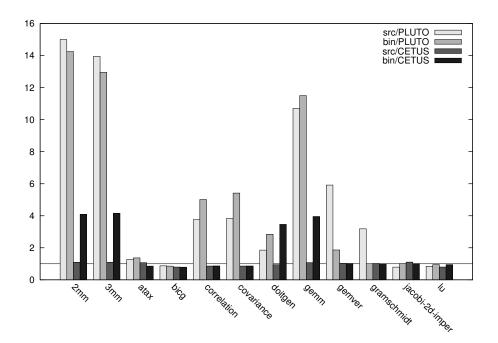

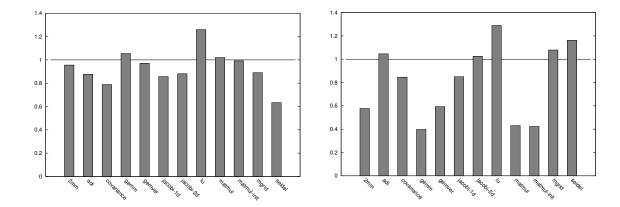

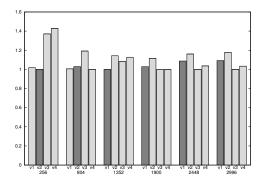

Figure 3: Parallélisation avec CETUS ou PLUTO depuis 1) le code source original 2) le code source extrait du programme binaire.

d'optimisation 02 et 03. Nous avons ensuite analysé les différents codes séquentiels résultats avec notre système. Toutes les boucles sont trouvées mais, avec un niveau d'optimisation avancé, une part non négligeable de ces boucles ne peut pas être traitée : 77 % peuvent être traitées au niveau 02, et 72 % au niveau 03. La plupart des problèmes proviennent des appels de fonctions qui compliquent l'analyse (même si celle-ci est intra-procédurale). Les transformations complexes de code sont également une source d'abandon de parallélisation.

L'analyse inter-procédurale et une étape d'inversion des transformations de codes, comme le déroulage de boucles, pourraient augmenter fortement la proportion des boucles parallélisables par notre système.

#### Code binaire ou code source?

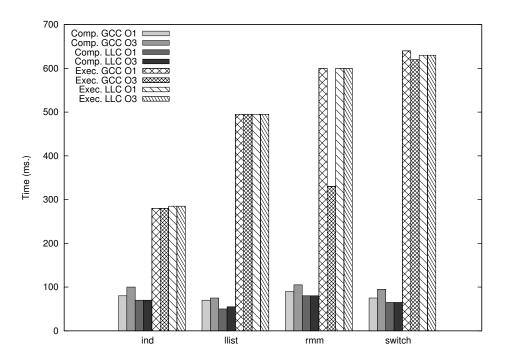

En Figure 3, nous présentons des accélérations obtenues sur une machine quadri-cœurs Intel Xeon W3520. CETUS et PLUTO sont comparés dans la figure lorsque la paral-lélisation est réalisée depuis le code source original du programme ou depuis le code source extrait du programme binaire par notre système.

On peut s'apercevoir que notre système permet en général une parallélisation du programme binaire à peu près aussi efficace que celle réalisée à partir du code source original du programme. L'analyse du programme est donc suffisamment précise pour permettre une parallélisation efficace et le système dynamique qui redirige l'exécution a un coût très raisonnable. On peut également noter que CETUS fonctionne mieux depuis le binaire car il bénéficie dans ce cas des simplifications réalisée lors de la compilation initiale du programme séquentiel.

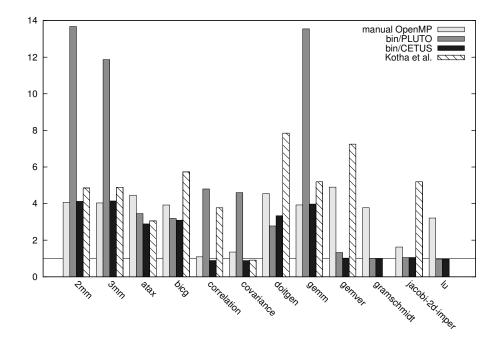

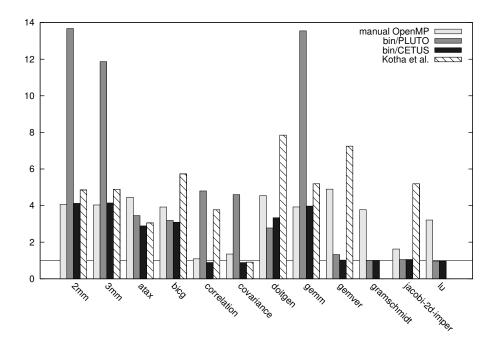

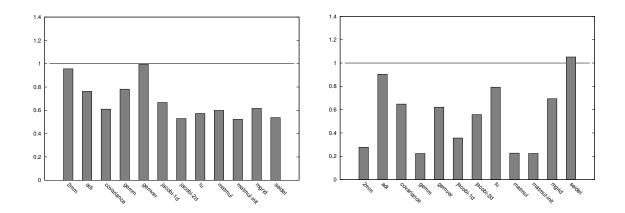

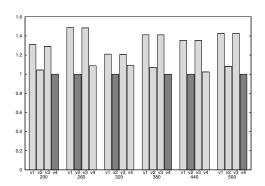

Figure 4: Comparaison de notre système à une parallélisation manuelle et à l'état de l'art.

#### Autres méthodes

Un graphe similaire est présenté en Figure 4, mais les deux paralléliseurs utilisés par notre système sont alors comparés à une parallélisation manuelle du code source original, ainsi qu'au système présenté par Kotha et al. dans [74]. Notre système, lorsqu'il s'appuie sur le paralléliseur PLUTO, est le seul capable de réaliser des transformations polyédriques. Cet avantage est décisif dans certains programmes tels que 2mm ou covariance. Cependant, dans d'autres programmes, les fonctions d'accès ou les transformations appliquées lors de la compilation du programme séquentiel ne nous permettent pas d'analyser ou de paralléliser aussi efficacement les nids de boucles. Notre système est également très dépendant de l'efficacité des paralléliseurs utilisés et ne parvient pas à atteindre de bonnes performances lorsque les paralléliseurs ne le permettent pas. C'est le cas par exemple avec lu ou jacobi-2d-imper.

#### **Extensions**

#### Codes paramétriques

Après l'analyse du programme, le code extrait est simplifié pour faciliter la parallélisation. La plupart des techniques de simplification sont exactes lorsque ni les accès mémoires, ni les bornes des boucles ne contiennent de paramètres. Dans le cas contraire, notre système émet des hypothèses qui lui permettent de simplifier les programmes contenant des paramètres. Si les bornes des boucles sont paramétriques, Kotha et al. ont proposé dans [74] de diviser la mémoire en tableaux disjoints en considérant l'adresse de base des accès comme indice pour distinguer les tableaux. Nous proposons

une technique similaire lorsque l'adresse de base des tableaux est un registre, ce qui arrive fréquemment lorsque la mémoire est allouée dynamiquement dans le programme original.

Lors de l'exécution du programme, des tests sont évalués pour s'assurer que les références pour lesquelles on a supposé qu'elles accèdent à des tableaux différents, le font effectivement. Ces tests paramétriques peuvent être générés automatiquement à l'aide d'outils tels que ISL [140]. Cette technique permet de paralléliser par exemple le programme swim de la suite SpecOMP 2001 [5]. Sur un processeur quadri-cœurs récent, notre système atteint une accélération de  $1,2 \times en$  comparaison à une accélération référence de  $1,5 \times en$

#### Références polynomiales

Jusque là, nous nous sommes principalement intéressés aux références mémoire linéaires. Il est pourtant fréquent de rencontrer des références non linéaires dans les programmes compilés, par exemple si des tableaux dynamiques sont utilisés. Afin de paralléliser ces programmes, nous proposons d'utiliser une technique basée sur l'expansion de Bernstein [31] afin de s'assurer à l'exécution que la boucle externe du nid ne porte pas de dépendance et peut donc être parallélisée.

Avec cette possibilité, notre système peut paralléliser des programmes tels que mgrid de la suite SpecOMP 2001. Sur le même processeur que précédemment, nous atteignons une accélération de  $1.8 \times$  en comparaison à l'accélération référence de  $3.1 \times$ . Comme pour l'exemple précédent, la référence consiste en une parallélisation manuelle dans laquelle un expert a indiqué que la parallélisation est possible, tandis que notre système est entièrement automatique.

#### Parallélisation sur place

Jusque là, chaque nid de boucle parallélisé est rajouté au code total du programme. Si un nid de boucle est parallélisé sans être transformé comme c'est le cas en présence d'accès non linéaires, il est possible de ne pas augmenter sensiblement la taille du programme en le parallélisant.

Pour cela, le composant d'observation qui redirige l'exécution vers les versions parallèles des nids de boucles va modifier le code binaire séquentiel lorsqu'un point d'arrêt est rencontré. Les fonctions présentes dans la librairie dynamique gèrent alors les threads qui exécutent simultanément le code séquentiel initial, réalisant la parallélisation. Les modifications réalisées par le composant d'observation, garantissent que l'exécution est correcte.

#### Conclusion

Nous avons présenté un système de parallélisation de code binaire. Ce système est l'approche statique de parallélisation, il est donc la première brique de notre approche générale. Notre système, même s'il est limité aux nids de boucles analysables et parallélisables statiquement, présente deux nouveautés principales : il est statique contrairement à la majorité des systèmes de parallélisation de code binaire proposés jusque là

Figure 5: Schéma général du sélecteur de versions.

et il est modulaire. Différents paralléliseurs source-à-source peuvent être utilisés, y compris des paralléliseurs polyédriques qui améliorent sensiblement la performance des programmes par rapport à l'existant.

Cette approche permet également d'étendre les applications du modèle polyédrique vers les programmes binaires, pour lesquels le format du code est a priori plus complexe.

Les détails sur les techniques présentées et leur implémentation sont disponibles dans le Chapitre 3.

## Sélection de Versions de Programmes

#### Introduction

Le deuxième système que nous proposons est un système hybride : il réalise certaines opérations au moment de la compilation du programme mais bénéficie également des informations disponibles au moment de son exécution. En exploitant ces différentes phases, notre système permet de sélectionner différentes versions de nids de boucles polyédriques en fonction du contexte d'exécution courant. Ce contexte d'exécution impacte la performance des programmes et consiste principalement en deux facteurs sur les architectures multi-cœurs modernes : l'équilibre de charge et la taille des données utilisées. Notre système se concentre donc sur ces deux facteurs.

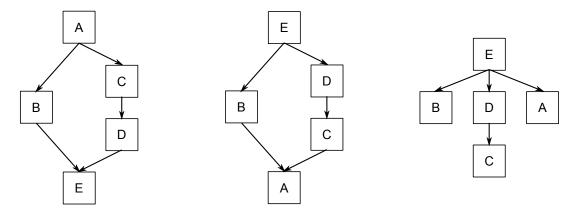

Comme présenté en Figure 5, les différentes versions des nids de boucles polyédriques sont générées lors de la compilation, chacune résultant de l'application d'optimisations différentes sur le nid de boucle original. Ces versions sont observées dans une phase de profilage, typiquement exécutée lors de l'installation du programme. À l'exécution, le résultat de ce profilage est combiné avec le contexte d'exécution observable lors de l'exécution du programme pour sélectionner une version supposée la plus performante.

#### Génération des Versions

Lors de nos tests, nous avons généré les versions en appliquant manuellement des transformations polyédriques différentes sur les programmes exemples. Les transformations diffèrent par l'ordonnancement des itérations, le nombre de niveaux de tuilage, et la taille des tuiles utilisées. Les paralléliseurs polyédriques automatiques peuvent facilement générer plusieurs versions d'un nid polyédrique en utilisant des heuristiques par exemple. La nature itérative de LetSee [105] fait de ce paralléliseur un très bon candidat pour générer automatiquement différentes versions d'un nid de boucles.

#### **Profilage**

Après avoir généré les versions, elles sont profilées dans une phase unique dédiée, typiquement exécutée lors de l'installation du programme. Il s'agit alors de mesurer l'impact de l'équilibre de charge et de la taille des données sur les performances de chaque version. Pour ne pas avoir à mesurer cette performance pour toutes les tailles de données possibles, nous approximons que l'ordre relatif des versions pour des grandes données est représentatif de l'ordre relatif des versions pour toutes les tailles de données. La précision de la sélection est ainsi amoindrie, mais en pratique, le système reste très efficace avec cette approximation en particulier pour les grandes données, où le temps de calcul est plus important.

Lors du profilage, il faut alors mesurer le temps nécessaire en moyenne pour exécuter une itération du nid pour les grandes données et pour les différents équilibres de charges possibles. Nous proposons deux stratégies différentes pour réaliser cette mesure.

#### Profilage 1

La première stratégie de profilage a pour objectif de mesurer la performance des versions dans des domaines d'itérations aussi similaires que possible. Pour contrôler l'équilibre de charge et la taille des données, les bornes du nid de boucles sont modifiées. Après avoir appliqué la transformation polyédrique, ces bornes de boucles sont supprimées et remplacées par des contraintes simples. Ces contraintes assurent que les boucles commencent à 0, que la boucle parallèle exécute par\_sz itérations, et que les autres boucles exécutent N\_min itérations. Ces deux nouveaux paramètres sont modifiés au cours du profilage pour mesurer des temps d'exécution pour des grandes données et pour contrôler le nombre d'itérations parallèles (et donc l'équilibre de charge).

Cette méthode est simple et fonctionne pour n'importe quel nid de boucle. Son inconvénient principal est qu'elle détruit les bornes des boucles et donc que certains effets de bords tels que le coût du contrôle sont mal évalués lors du profilage.

#### Profilage 2

La deuxième méthode de profilage préserve le nid de boucle dans son état initial. Le nombre de threads actifs est contrôlé par l'utilisation de la méthode omp\_set\_num\_threads d'OpenMP. La taille des données est contrôlée par les paramètres présents dans les bornes des boucles du nid.

Afin de déterminer comment augmenter la taille du domaine d'itération à l'aide des paramètres existants, nous privilégions une approche polyédrique. Un nouveau paramètre N\_min est considéré. Il représente la taille d'un hypercube qui doit pouvoir rentrer dans le polyèdre du domaine d'itération pour garantir qu'un certain nombre d'itérations seront exécutées. Le lien entre N\_min et les paramètres du nid de boucle est obtenu grâce aux outils polyédriques tels que PIP [45]. Le résultat pour chaque paramètre est une expression qui définit la valeur du paramètre en fonction de N\_min pour garantir qu'un certain nombre d'itérations seront exécutées par le nid de boucles.

#### Utilisation du code de profilage

Quelle que soit la méthode de profilage choisie, chaque version disponible est exécutée pour une grande taille de données, et une mesure de temps d'exécution est réalisée pour chaque nombre de threads actifs. Le résultat de cette étape est stocké dans une table de classement qui sera utile pour prédire la performance de chacune des versions.

#### Sélection des Versions

Une fois le profilage réalisé, la sélection des versions peut avoir lieu avant chaque exécution du nid de boucles. Pour ce faire, le temps d'exécution de chacune des versions dans le contexte d'exécution courant est prédit. Cette prédiction est réalisée grâce à un nid de boucle dédié, le *nid de prédiction*, qui mesure l'équilibrage de charge courant.

#### Nombre d'itérations

Le nid de prédiction est en charge de mesurer le nombre de threads actifs pour chaque itération du nid de boucles. C'est de cette mesure que l'équilibre de charge sera déduit plus tard.

Le nid de prédiction est construit à partir du nid de boucle exécuté. Le contenu de la boucle parallèle est remplacé par un polynôme d'Ehrhart qui définit le nombre d'itérations exécutées dans l'itération courante de la boucle parallèle. Ce nombre d'itérations est assigné à un compteur propre au thread qui le calcule. À la fin de l'exécution du nid de prédiction, il est donc possible de consulter le nombre d'itérations exécutées par chaque thread.

#### Temps d'exécution

En faisant l'hypothèse que le temps d'exécution par itération est constant, on peut facilement déduire la mesure inverse du nombre d'itérations exécutées par chaque thread, c'est à dire le nombre de threads actifs lors de l'exécution de chacune des itérations. Pour cela, il suffit de trier les mesures obtenues par le nid de prédiction en ordre décroissant et de considérer les différences entre deux entrées successives. Par exemple, si on mesure qu'un thread a exécuté trois itérations et que l'autre thread en a exécuté 5, on peut déduire que les deux threads ont été actifs pendant l'exécution de trois itérations alors qu'un seul thread a été actif pendant l'exécution de deux itérations.

On appelle NC le nombre de cœurs de calcul disponibles,  $Nit_t^v$  le nombre d'itérations exécutées par t threads (le résultat du nid de prédiction de la version v), et  $ET_t^v$  le temps d'exécution d'une itération en utilisant la version v et t threads (le résultat du profilage). Le temps d'exécution prédit pour la version v est alors défini par :

$$\sum_{t=0}^{NC} (t \times Nit_t^v \times ET_t^v)$$

En utilisant cette formule simple, on peut prédire un temps d'exécution pour chaque version juste avant d'exécuter le calcul. Il suffit alors d'effectuer le calcul en utilisant la version pour laquelle le temps d'exécution prédit est le plus petit.

## Évaluation

L'évaluation de notre système a été réalisée sur trois machines, décrites dans le Chapitre 4, en utilisant différentes versions de programmes, dont les détails sont également disponibles dans ce chapitre. Les versions sont évaluées dans différents contextes qui se distinguent par la taille des données utilisées et par le nombre de cœurs de calculs disponibles sur chacun des ordinateurs considérés.

#### Influence du contexte

En évaluant les versions des programmes pour plusieurs tailles de données, on s'aperçoit que le contexte d'exécution influence les programmes de différentes manières. En premier lieu, et de façon évidente, on peut remarquer que la machine qui exécute le programme influence la performance de ce programme. Ce n'est alors pas toujours la même version du programme qui est la plus efficace selon l'ordinateur considéré. Ensuite, la taille des données a aussi un impact sur la performance du programme. Selon la taille des données, ce n'est pas toujours la même version qui est la plus rapide. Enfin, le nombre de cœurs de calculs disponible influence également la performance relative des versions.

Différents exemples chiffrés sont présentés dans la section expérimentale du Chapitre 4.

#### Temps d'exécution

Afin d'évaluer la performance de notre système de sélection, nous avons mesuré l'accélération des programmes qu'il réalise dans différents contextes d'exécution par rapport à un système de sélection de versions parfait. Les résultats sont présentés dans la Table 1. Un résultat de 100% indique une performance maximale en considérant les versions disponibles. La performance de chacune des stratégies de profilage est présentée avec celle de la meilleure version statique. Celle-ci est la plus rapide dans tous les contextes d'exécution testés, elle a été déterminée après avoir testé toutes les versions. Notre système atteint des performances comparables à cette meilleure version statique, et arrive même à la dépasser dans certains cas. Le surcoût du nid de prédiction est considéré dans ces mesures. On peut déduire de ces mesures que notre système de sélection est efficace et permet de bénéficier d'accélérations spécifiques à certains contextes d'exécutions.

| Processeur   | Programme           | Stratégie 1 | Stratégie 2 | Meilleure version |

|--------------|---------------------|-------------|-------------|-------------------|

| 1 TOCCSSC GI | Trogramme           | Diracegie 1 | _           | statique          |

| 1            | 2mm                 | 100.0 %     | 98.9 %      | 100.0 %           |

| ı            | adi                 | 99.6 %      | 98.7 %      | 97.5 %            |

|              | covariance          | 96.6 %      | 95.8 %      | 99.7 %            |

| 1            | gemm                | 93.4 %      | 84.7 %      | 93.5~%            |

|              | gemver              | 80.6 %      | 98.3 %      | 91.6 %            |

| Corei7       | jacobi-1d           | 99.5 %      | 99.5 %      | 99.9 %            |

| Corer        | jacobi-2d           | 90.2 %      | 94.8 %      | 99.6 %            |

| ı            | lu                  | 91.2 %      | -           | 98.3 %            |

|              | matmul              | 98.5 %      | 97.9 %      | 98.5 %            |

|              | ${\tt matmul-init}$ | 100.0 %     | 97.6 %      | 100.0 %           |

|              | mgrid               | 97.0 %      | 99.9 %      | 97.0 %            |

|              | seidel              | 99.5 %      | 99.8 %      | 99.6 %            |

|              | 2mm                 | 100.0 %     | 100.0 %     | 100.0 %           |

| ı            | adi                 | 99.1 %      | 99.6 %      | 97.3 %            |

|              | covariance          | 99.8 %      | 99.8 %      | 99.8 %            |

| ı            | gemm                | 97.8 %      | 96.5 %      | 96.7~%            |

|              | gemver              | 99.7 %      | 99.4 %      | 99.8 %            |

| 04           | jacobi-1d           | 99.6 %      | 99.6 %      | 100.0 %           |

| Opteron      | jacobi-2d           | 100.0 %     | 98.5 %      | 100.0 %           |

| ı            | lu                  | 100.0 %     | _           | 100.0 %           |

| ı            | matmul              | 100.0 %     | 96.9 %      | 100.0 %           |

|              | matmul-init         | 100.0 %     | 100.0 %     | 100.0 %           |

| ı            | mgrid               | 96.2 %      | 99.0 %      | 98.5 %            |

| ı            | seidel              | 98.9 %      | 99.5 %      | 98.3 %            |

|              | 2mm                 | 100.0 %     | 100.0 %     | 100.0 %           |

|              | adi                 | 98.7 %      | 99.5 %      | 97.5 %            |

| ı            | covariance          | 99.9 %      | 99.9 %      | 99.9 %            |

| ı            | gemm                | 99.2 %      | 97.2 %      | 96.9 %            |

| ı            | gemver              | 99.7 %      | 99.1 %      | 99.8 %            |

| DI           | jacobi-1d           | 99.7 %      | 99.7 %      | 100.0 %           |

| Phenom       | jacobi-2d           | 99.4 %      | 98.7 %      | 100.0 %           |

|              | lu                  | 100.0 %     | _           | 100.0 %           |

|              | matmul              | 100.0 %     | 100.0 %     | 100.0 %           |

|              | matmul-init         | 100.0 %     | 100.0 %     | 100.0 %           |

|              | mgrid               | 95.9 %      | 99.7 %      | 98.1 %            |

|              | seidel              | 99.0 %      | 98.9 %      | 99.0 %            |

Table 1: Accélération des deux stratégies de profilage et de la meilleure version statique par rapport à un mécanisme parfait de sélection de versions.

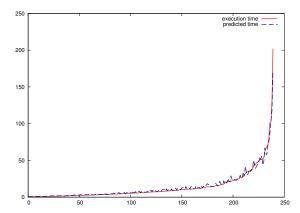

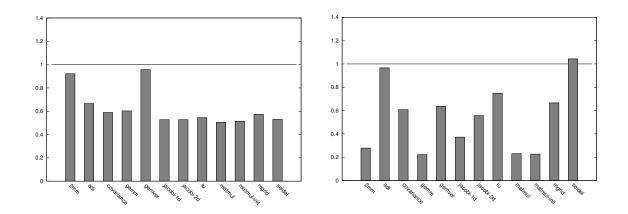

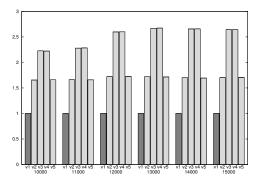

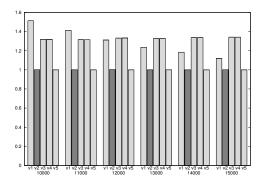

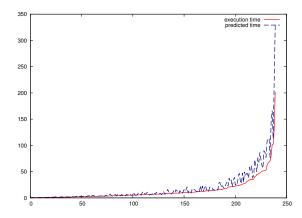

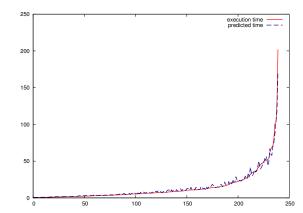

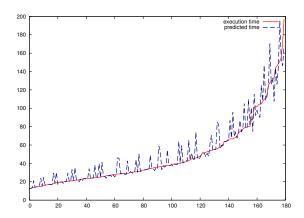

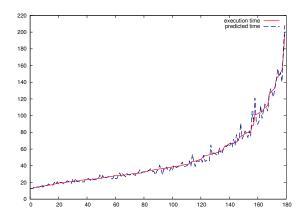

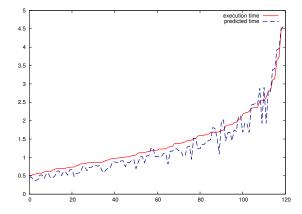

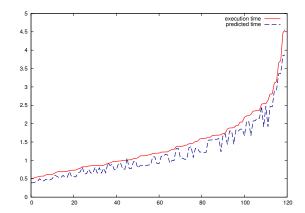

Figure 6: Temps d'exécution (en secondes) réel et prédit de toutes les versions du programme 2mm dans tous les contextes testés, trié par le temps d'exécution réel. Sur Core i7 avec la stratégie 1.

Figure 7: Temps d'exécution (en secondes) réel et prédit de toutes les versions du programme 2mm dans tous les contextes testés, trié par le temps d'exécution réel. Sur Core i7 avec la stratégie 1.

#### Précision

Même si la performance atteinte en utilisant les deux stratégies de profilage est comparable, nous avons évalué la précision de chacune de ces stratégies. Pour ce faire nous présentons en Figure 6 et 7 le temps d'exécution réel et prédit de chacune des stratégies pour toutes les versions dans tous les contextes d'exécution testés pour un programme sur un processeur. Le trait plein indique le temps d'exécution réel, le trait pointillé indique le temps d'exécution prédit. Les versions dans les différents contextes d'exécutions sont présentées horizontalement. Le temps d'exécution est représenté sur la direction verticale. Les mesures sont triées par temps d'exécution réel croissant. On peut s'apercevoir que les deux courbes sont proches : le temps prédit est très proche du temps d'exécution réel. La stratégie 2 semble cependant plus précise. D'autres mesures similaires sont présentées dans le Chapitre 4.

#### Conclusion

Nous avons présenté un système de sélection de version hybride qui constitue la deuxième brique de notre approche générale. Bien que limité aux boucles affines, il exploite à la fois la période de compilation et celle de l'exécution du programme pour effectuer une sélection de versions parallèles efficace et précise dès la première exécution du nid. Il permet ainsi de bénéficier du contexte d'exécution courant pour accélérer les programmes par rapport à une version unique.

Comme il exploite le modèle polyédrique, notre système peut être vu comme une extension de ce modèle vers l'amélioration de la performance des programmes en profitant des particularités des contextes d'exécution.

Le Chapitre 4 présente les détails de la méthode, les implémentations réalisées, et d'autres mesures pour argumenter de la validité de notre approche.

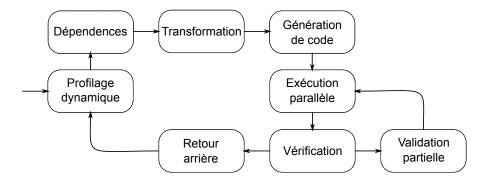

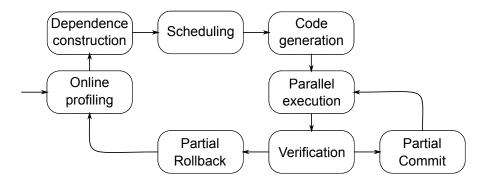

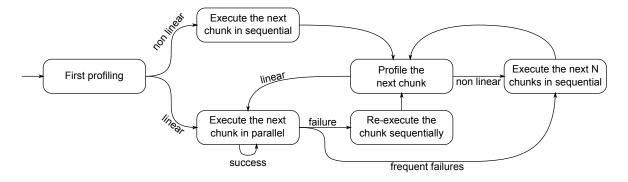

Figure 8: Les différentes étapes de notre paralléliseur spéculatif.

## Parallélisation Spéculative

#### Introduction

Le troisième mécanisme que nous proposons est dynamique, il exploite principalement la période d'exécution des programmes pour les paralléliser. Il consiste en un système de parallélisation spéculative capable d'appliquer des transformations polyédriques sur les nids de boucle pour les paralléliser efficacement même s'ils ne sont pas analysable statiquement.

Les systèmes spéculatifs sont intéressants car ils permettent la parallélisation de codes complexes qui contiennent par exemple des accès pointeurs impossibles à analyser statiquement. Ils permettent également le traitement de programmes qui ne sont parallèles que dans certaines phases de leur exécution. L'apport principal de notre méthode est la possibilité d'appliquer des transformations polyédriques de façon spéculative.

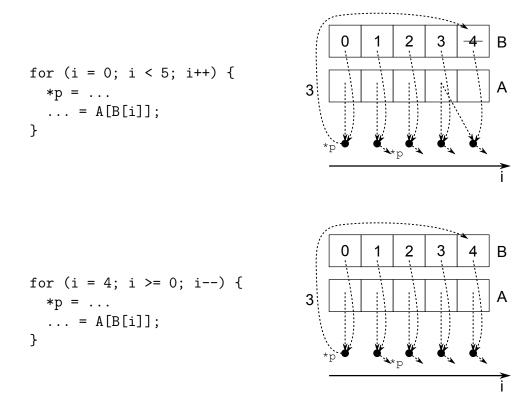

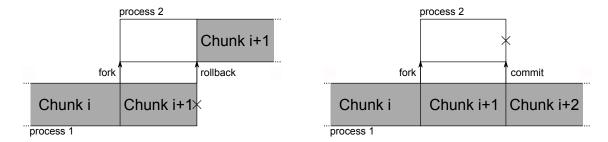

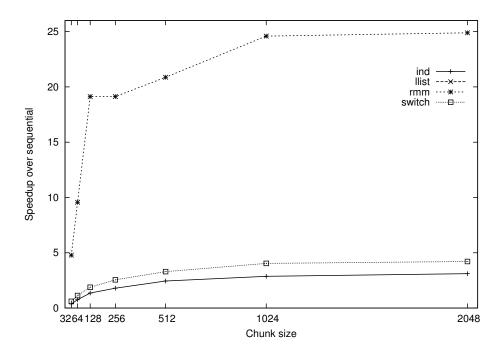

La Figure 8 présente les différentes étapes d'un tel système. Tout d'abord, le programme est observé sur une courte période, plusieurs éléments tels que les accès mémoires, la valeur de certains scalaires, et les bornes de certaines boucles sont instrumentées. Si ces éléments peuvent être décrits par une fonction linéaire, alors le système suppose que cette caractérisation sera valable pour toute l'exécution du programme. Partant de cette hypothèse, les dépendances du programmes sont construites puis une transformation polyédrique est choisie. Le code correspondant est alors généré puis exécuté. Pendant l'exécution parallèle, les hypothèses émises par le système sont vérifiées et, si elles s'avèrent incorrectes, l'exécution est partiellement annulée avant de recommencer un cycle de parallélisation.

## Profilage en-ligne et Dépendances

Lorsqu'un nid de boucle intéressant est exécuté, la première tâche réalisée par le système est d'observer le comportement de ce nid. Cette observation a pour principal objectif de déterminer si les accès mémoires peuvent être décrits par des fonctions linéaires, condition préalable à l'application du modèle polyédrique. Certains scalaires sont fréquemment la source de nombreuses dépendances dans les nids de boucles. Dans certains cas ils peuvent être traités statiquement, par privatisation par exemple. Les codes complexes que notre système considère contiennent fréquemment des scalaires qui

ne peuvent pas être traités statiquement mais dont la valeur est une fonction linéaire des indices des boucles englobantes. Ces valeurs sont donc également observées afin de supprimer les dépendances associées aux scalaires et permettre la parallélisation. Pour permettre l'implémentation d'un mécanisme transactionnel, le nombre d'itérations des boucles while est également observé et exprimé sous forme de fonction linéaire lorsque c'est possible.

#### **Profilage**

Les adresses accédées sont donc instrumentées ainsi que la valeur des scalaires qui provoquent des dépendances qui ne peuvent pas être éliminées statiquement. De la même façon, le nombre d'itérations des boucles while est également mesuré pour former une fonction linéaire lorsque c'est possible. Cette instrumentation est exécutée pendant trois itérations de chaque niveau de boucle, le temps de mesurer un nombre suffisant de valeurs pour construire les fonctions linéaires. Cependant, dans certains cas, il est nécessaire d'observer les boucles pendant une plus longue période. C'est le cas par exemple si un accès mémoire est présent dans un test qui n'est pas pris à chaque itération. Si des données d'instrumentation sont manquantes après trois itérations, le profilage continue jusqu'à au plus dix itérations.

#### Construction des dépendances

Lorsque tous les éléments profilés sont identifiés comme étant linéaires, le système fait l'hypothèse que ce comportement est représentatif du comportement général de l'application. C'est l'aspect spéculatif du système. Sous cette hypothèse, qui sera vérifiée plus tard, les dépendances du nid de boucle sont construites. Ces dépendances sont représentées sous forme de polyèdres de dépendance qui sont une représentation compacte mais exacte des dépendances dans le cadre polyédrique. Ces dépendances sont utilisées plus tard pour choisir une transformation pour le nid de boucle.

#### Ordonnancement

Les dépendances construites sont spéculatives. Si les éléments observés comme étant linéaires pendant le profilage en ligne le sont effectivement, alors ces dépendances sont celles qui ont lieu lors de l'exécution du nid. Il faut alors choisir une transformation polyédrique qui respecte ces dépendances. Cette transformation sera correcte et ne nécessitera pas de retour arrière si les dépendances spéculatives sont correctes durant toute l'exécution du programme.

#### Profilage hors-ligne

Le choix d'une transformation polyédrique en fonction de dépendances est extrêmement complexe et les techniques existantes ont un coût qui ne peut pas être facilement amorti dans un système dynamique. Notre système effectue donc un profilage hors-ligne (avant l'exécution du programme) afin d'étudier le comportement des éléments qui seront profilés plus tard lors de l'exécution du programme par la phase de profilage en-ligne.

Si, lors du profilage hors-ligne, il s'avère que ces éléments sont majoritairement linéaires, alors les dépendances observées sont reconstruites et un ensemble de transformations possibles est identifié. Ces transformations sont alors embarquées dans le programme séquentiel et pourront être sélectionnées si les dépendances spéculatives le permettent.

#### Ordonnancements génériques