Nº d'ordre: xxxx

### École Doctorale de Physique et Chimie-Physique de l'Université de Strasbourg

**UDS**

# **THÈSE**

### présentée pour obtenir le grade de

### Docteur de l'Université de Strasbourg

Discipline: Électronique, Électrotechnique et Automatique Spécialité : Instrumentation et Microélectronique

par

## Liang ZHANG

# Development of a CMOS Pixel Sensor for the Outer Layers of the ILC Vertex Detector

soutenue publiquement le 30 septembre 2013 devant le jury:

Directeur de thèse: YANN HU Professeur, UDS, Strasbourg

Rapporteur externe: MICHEL PAINDAVOINE Professeur, UDB, Bourgogne

Rapporteur externe: JEAN-FRANÇOIS GENAT Ingénieur de recherche, HDR, LPNHE, Paris

Examinateur: WILFRIED UHRING Professeur, UDS, Strasbourg

Membre invité: MARC WINTER Directeur de recherche, IPHC, Strasbourg

### Acknowledgements

This dissertation was made possible by the help of many individuals during the last four years in France. Foremost, I would like to thank China Scholarship Council (CSC) for the financial support during my Ph.D. study and research in University of Strasbourg, France and Institut Pluridisciplinaire Hubert Curien (IPHC), CNRS.

I would like to express my sincere gratitude to my advisor Prof. Yann Hu for giving the opportunity to work in the institute and for his motivation, enthusiasm, and immense knowledge. His guidance helped me in all the time of research and writing of this thesis.

Beside my advisor, my sincere thanks also go to Dr. Christine Hu-Guo, the director of microelectronic group, for leading me working on the exciting project and for giving me insightful comments. I would like to thank Dr. Frederic Morel for his fruitful discussions and suggestions during this work.

I would like to thank Prof. Jerome Baudot for his insightful comments on the physical part of this work. I would also like to thank Gilles Claus, Kimmo Jaaskelainen, Mathieu Goffe and Mathieu Specht for their help with the testbench. And I would like to thank all of the members of the PIC-SEL group: Abdelkader Himmi, Andrei Dorokhov, Auguste Besson, Christian Illinger, Claude Colledani, Gregory Bertolone, Guy Doziere, Hung Pham, Isabelle Vallin, Marc Winter, Rachid Sefri, Sylviane Molinet, Tianyang Wang, Wei Zhao, Xiaochao Fang and Yang Zhou for their assistance in my work.

Last but not the least, I would like to thank my parents and sister for their unconditional support throughout my life. Especially I would like to thank my wife, Dr. Wei Yan, for her patience, understanding and encouragement that made me complete the Ph.D. work. I am very grateful to her.

# Contents

| $\mathbf{C}$ | onten                  | iii                                                |

|--------------|------------------------|----------------------------------------------------|

| Li           | st of                  | Figures                                            |

| Li           | st of                  | Tables xi                                          |

| A            | bstra                  | xiii                                               |

| R            | ésum                   | en Français xv                                     |

| In           | trodu                  | ction                                              |

| 1            | ILC                    | Vertex Detector 1                                  |

|              | 1.1                    | The ILC Physics Programme                          |

|              |                        | 1.1.1 The ILC Machine                              |

|              | 1.2                    | ILD at ILC                                         |

|              |                        | 1.2.1 The ILD Layout                               |

|              | 1.3                    | Vertex Detector                                    |

|              |                        | 1.3.1 Requirements                                 |

|              |                        | 1.3.2 Geometries                                   |

|              |                        | 1.3.3 Sensor Technologies                          |

|              |                        | 1.3.4 CMOS Pixel Sensors for VTX                   |

|              | 1.4                    | Summary                                            |

|              | Bibli                  | ography                                            |

| 2            | $\mathbf{C}\mathbf{M}$ | OS Pixel Sensors for Charged Particle Detection 17 |

|              | 2.1                    | Detection Principle                                |

<u>iv</u> CONTENTS

|   | 2.2  | CPS A   | Architecture                             | 19        |

|---|------|---------|------------------------------------------|-----------|

|   |      | 2.2.1   | Pixel Circuit                            | 20        |

|   |      | 2.2.2   | Signal Processing Circuit                | 26        |

|   | 2.3  | State-o | of-the-art CPS                           | 30        |

|   |      | 2.3.1   | MIMOSA 26                                | 31        |

|   |      | 2.3.2   | ULTIMATE                                 | 33        |

|   | 2.4  | Sensor  | Concept for the ILD Vertex Detector      | 36        |

|   |      | 2.4.1   | Sensor Equipping the Innermost Layer     | 36        |

|   |      | 2.4.2   | Sensor Equipping the Outer Layers        | 38        |

|   | 2.5  | Summ    | ary                                      | 40        |

|   | Bibl | iograph | y                                        | 41        |

| 3 | Cal  | T       | evel Analog-to-Digital Converter for CPS | 45        |

| 3 | 3.1  |         | cations of A/D Converters                | <b>45</b> |

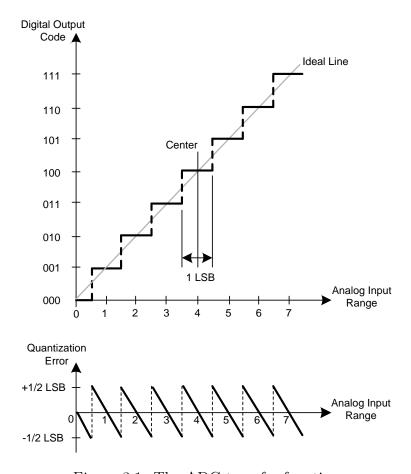

|   | 3.1  | 3.1.1   | Quantization Error                       | 45<br>45  |

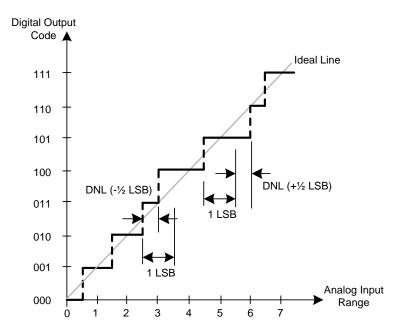

|   |      | 3.1.2   | Differential Nonlinearity                | 47        |

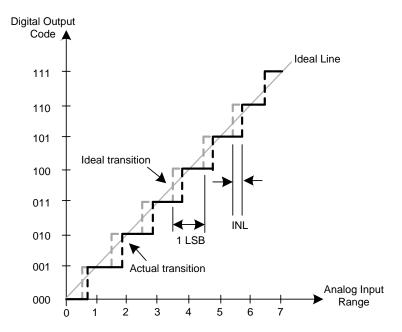

|   |      | 3.1.3   | Integral Nonlinearity                    | 48        |

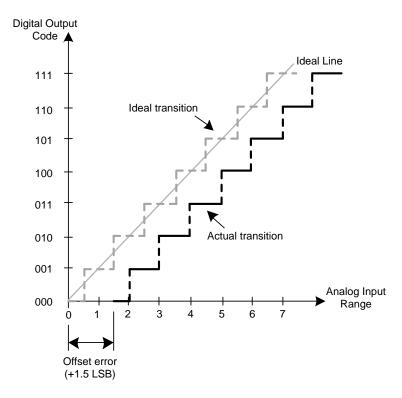

|   |      | 3.1.4   | Offset Error                             | 49        |

|   |      | 3.1.5   | Signal-to-Noise ratio                    | 49        |

|   |      | 3.1.6   | Noise                                    | 50        |

|   |      | 3.1.7   | Settling Time                            | 52        |

|   | 3.2  |         | Reduction Techniques                     | 52        |

|   | J.2  | 3.2.1   | Offset Compensation                      | 52        |

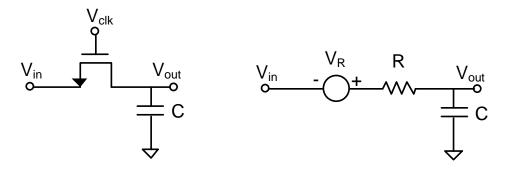

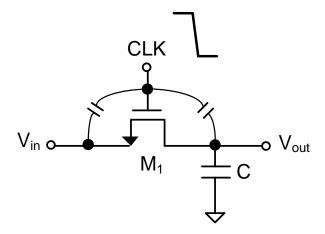

|   |      | 3.2.2   | Sampling Switches                        | 55        |

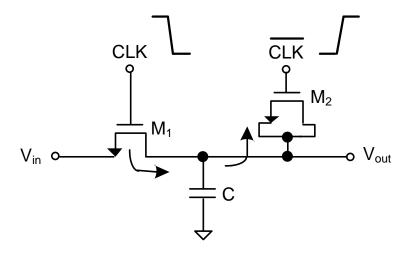

|   | 3.3  | 9       | Converter Architectures                  | 59        |

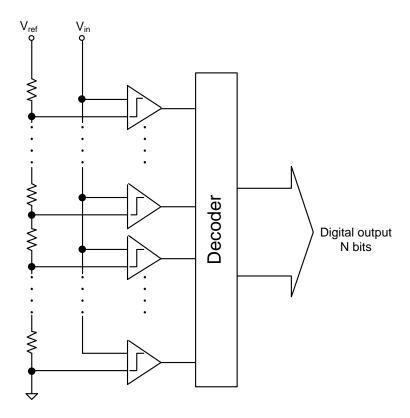

|   |      | 3.3.1   | Flash ADC                                | 59        |

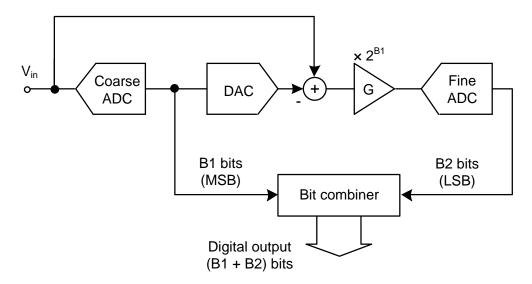

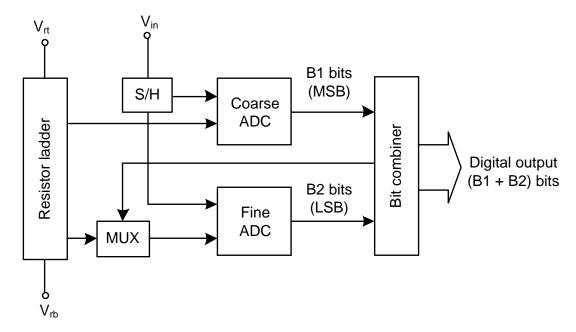

|   |      | 3.3.2   | Two-Step ADC                             | 60        |

|   |      | 3.3.3   | Subranging ADC                           | 61        |

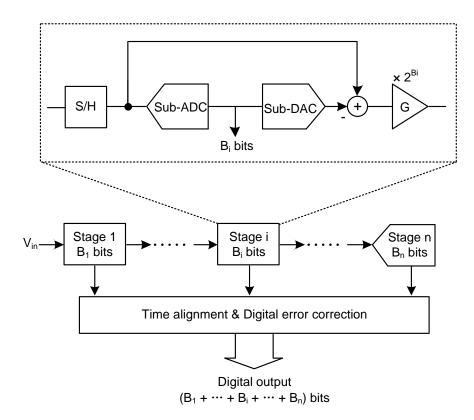

|   |      | 3.3.4   | Pipeline ADC                             | 63        |

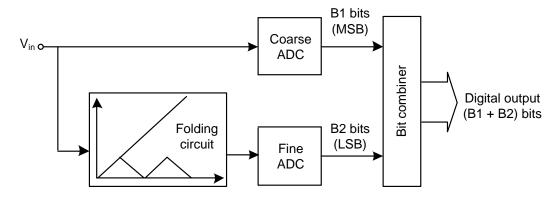

|   |      | 3.3.5   | Folding ADC                              | 64        |

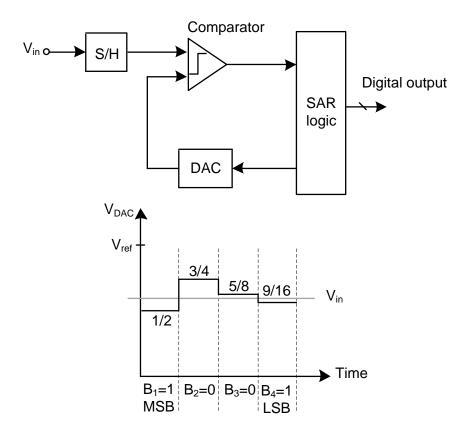

|   |      | 3.3.6   | Successive Approximation Register ADC    | 65        |

|   |      | 3.3.7   | Sigma-Delta ADC                          | 66        |

|   | 3.4  | Colum   | an-Level ADC Suitable to Vertex Detector |           |

CONTENTS

|   | 3.5  | Summary                                      |

|---|------|----------------------------------------------|

|   | Bibl | iography                                     |

| 4 | Des  | ign of a Sensor Prototype 75                 |

|   | 4.1  | Global Architecture                          |

|   | 4.2  | Pixel Circuit                                |

|   | 4.3  | Column-Level ADC                             |

|   |      | 4.3.1 Design Requirements                    |

|   |      | 4.3.2 Operation principle                    |

|   |      | 4.3.3 Optimal Power Saving                   |

|   |      | 4.3.4 Sample-and-hold                        |

|   |      | 4.3.5 Comparator                             |

|   |      | 4.3.6 Digital Logic                          |

|   |      | 4.3.7 DAC                                    |

|   | 4.4  | Simulation Results and Layout                |

|   | 4.5  | Summary                                      |

|   | Bibl | iography                                     |

| 5 | Fyr  | perimental Results 111                       |

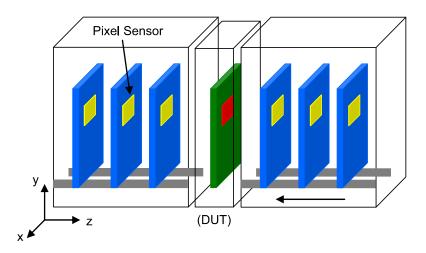

| J | 5.1  | Test Board and Setup                         |

|   | 5.2  | Test Results                                 |

|   | 9.2  | 5.2.1 Noise Performance                      |

|   |      | 5.2.1 Noise l'enformance                     |

|   |      | 5.2.3 ADC Performance                        |

|   | 5.3  | Summary                                      |

|   |      | iography                                     |

|   | וטוע | lography                                     |

| 6 | Imp  | provements on MIMOSA 31                      |

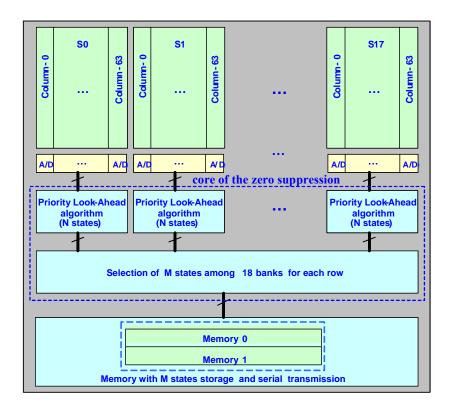

|   | 6.1  | Zero Suppression for MIMOSA 31               |

|   |      | 6.1.1 Physical Characteristics               |

|   |      | 6.1.2 Hit Recognition                        |

|   |      | 6.1.3 Data Sparsification Algorithm          |

|   |      | 6.1.4 Separated Sparse Banks in Pixel Matrix |

|   | 6.2  | Self-Timed ADC                               |

vi CONTENTS

|             |       | 6.2.1     | Architecture Design             | 131       |

|-------------|-------|-----------|---------------------------------|-----------|

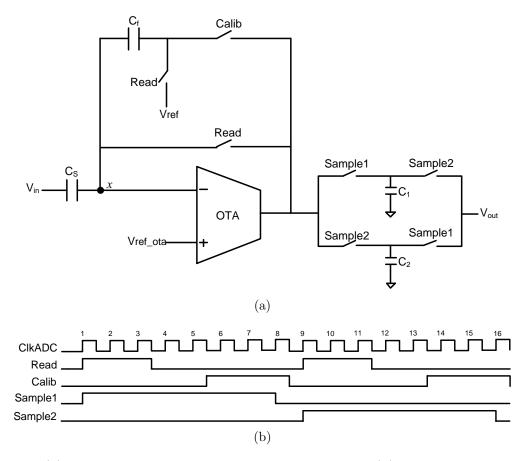

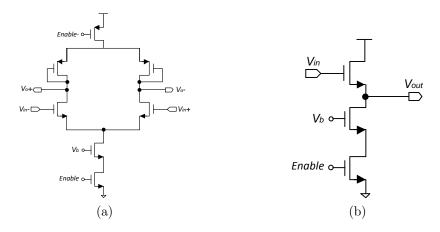

|             |       | 6.2.2     | Enhanced S/H Circuit            | 132       |

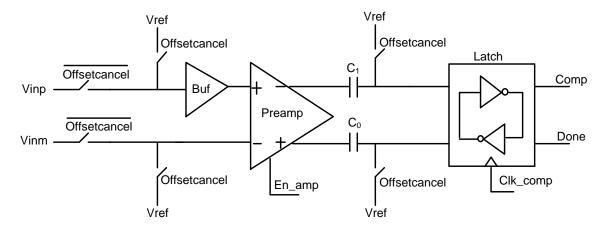

|             |       | 6.2.3     | Self-Timed Comparator           | 135       |

|             |       | 6.2.4     | Simulation Results              | 139       |

|             | 6.3   | Extend    | ded Self-Timed Discriminator    | 140       |

|             | 6.4   | Summ      | ary                             | 142       |

|             | Bibli | iograph   | y                               | 144       |

|             |       |           | and Perspectives  infigurations | 145 $151$ |

| <b>/1</b> . |       |           | _                               |           |

|             |       |           | _ID Register                    |           |

|             | A.2   | BIAS_     | _DAC Register                   | 152       |

|             | A.3   | PATT      | _LINE Register                  | 153       |

|             | A.4   | DIS_A     | ADC Register                    | 153       |

|             | A.5   | PIX_S     | SEQ Register                    | 153       |

|             | A.6   | $ADC_{-}$ | _SEQ Register                   | 154       |

|             |       |           |                                 |           |

# List of Figures

| 1    | Géométrie d'un détecteur de vertex. A gauche: 5 couches simples (VTX-            |

|------|----------------------------------------------------------------------------------|

|      | SL). A droite: 3 couches doubles (VTX-DL) xvi                                    |

| 2    | Schéma de principe du capteur à pixels CMOS proposé xvii                         |

| 3    | Microphotographie du capteur                                                     |

| 1.1  | Cross sections of physics processes as a function of the collision energy. $ 2 $ |

| 1.2  | Schematic layout of the International Linear Collider                            |

| 1.3  | Illustration of the pinch effect in bunch collisions                             |

| 1.4  | Bunch timing scheme of the ILC                                                   |

| 1.5  | Schematic view of the ILD detector concept                                       |

| 1.6  | Quadrant of the ILD detector concept                                             |

| 1.7  | Vertex detector geometries. Left: 5 single-sided ladders (VTX-SL). Right:        |

|      | 3 double-sided ladders (VTX-DL)                                                  |

| 2.1  | CMOS sensor operation principle                                                  |

| 2.2  | A simplified diagram of the CMOS pixel sensor                                    |

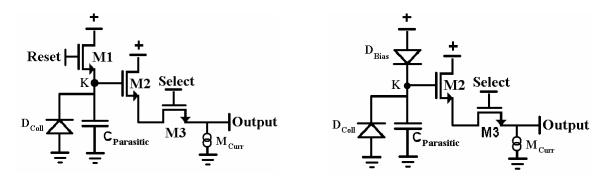

| 2.3  | Structure of the 3T pixel (left) and self-biased (SB) pixel (right)              |

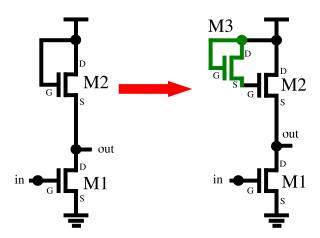

| 2.4  | Common source amplifier (left) and improved amplifier (right)                    |

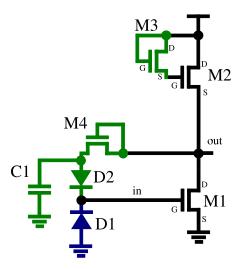

| 2.5  | Improved common source amplifier with feedback                                   |

| 2.6  | In-pixel CDS and enhanced CS amplifier with feedback                             |

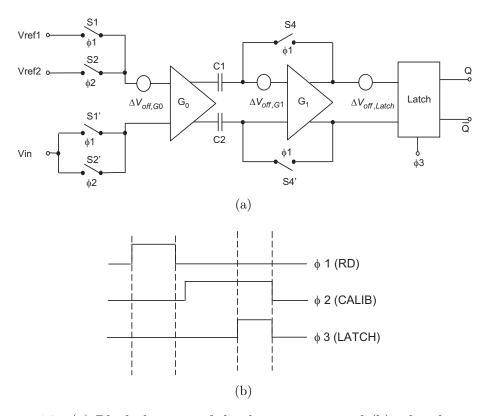

| 2.7  | (a) Block diagram of the discriminator and (b) related timing                    |

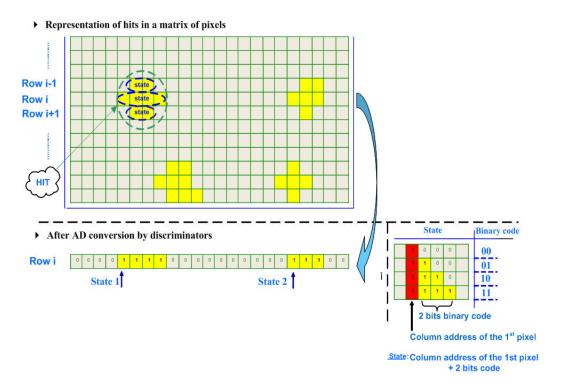

| 2.8  | Hit recognition and encoding of the pixels                                       |

| 2.9  | Block diagram of the zero suppression                                            |

| 2.10 | EUDET beam telescope                                                             |

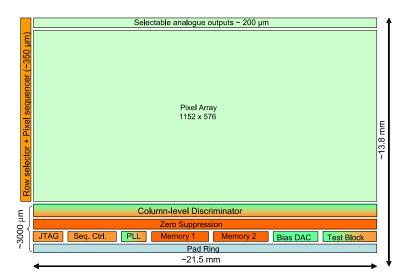

| 2.11 | Block diagram of MIMOSA-26                                                       |

viii LIST OF FIGURES

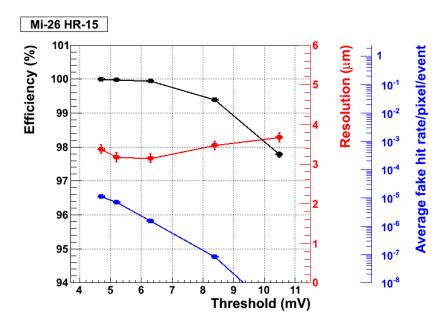

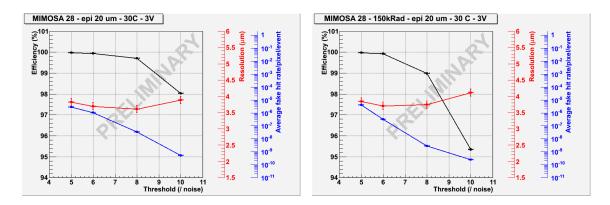

| 2.12 | MIMOSA-26 beam test results obtained at the CERN-SPS with $\sim 120~\text{GeV}$               |    |

|------|-----------------------------------------------------------------------------------------------|----|

|      | charged particles. The detection efficiency (black curve), the fake hit rate                  |    |

|      | (blue curve) and the single point resolution (red curve) are evaluated with                   |    |

|      | various discriminator thresholds                                                              | 33 |

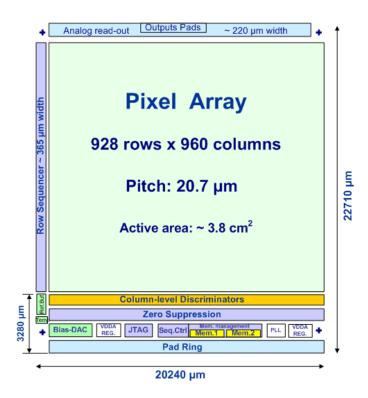

| 2.13 | Block diagram of ULTIMATE                                                                     | 34 |

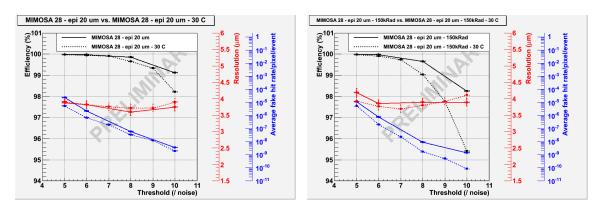

| 2.14 | Beam test results of ULTIMATE with power supply of 3.3 V, before (left)                       |    |

|      | and after (right) exposure to a dose of 150 kRads                                             | 35 |

| 2.15 | Beam test results of ULTIMATE with power supply of 3 V, before (left)                         |    |

|      | and after (right) exposure to a dose of 150 kRads                                             | 35 |

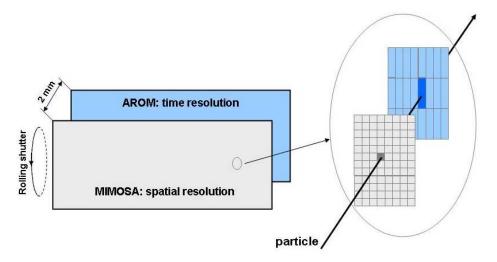

| 2.16 | Schematic of the combination of AROM (elongated pixels for time resolu-                       |    |

|      | tion) and MIMOSA (square pixels for spatial resolution) sensors equipping                     |    |

|      | the double-sided ladder                                                                       | 37 |

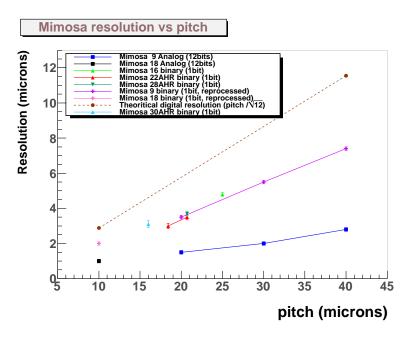

| 2.17 | Resolution vs pixel pitch                                                                     | 39 |

| 3.1  | The ADC transfer function                                                                     | 46 |

| 3.2  | Differential nonlinearity (DNL)                                                               | 47 |

| 3.3  | Integral nonlinearity (INL)                                                                   | 48 |

| 3.4  | Offset error                                                                                  | 49 |

| 3.5  | Simple sampling circuit (left) and thermal noise equivalent circuit (right). $\boldsymbol{.}$ | 51 |

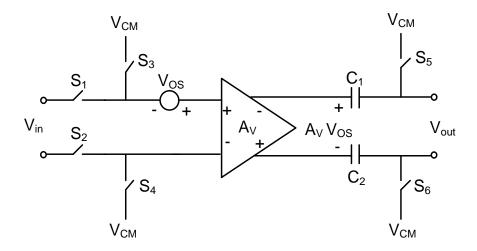

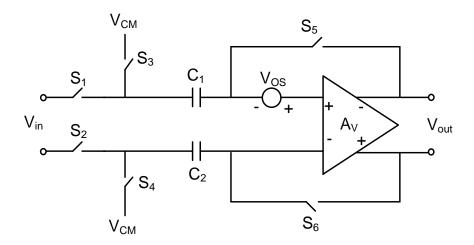

| 3.6  | Output offset storage architecture                                                            | 53 |

| 3.7  | Input offset storage architecture                                                             | 54 |

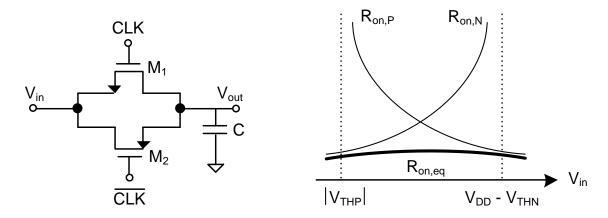

| 3.8  | CMOS switch (left) and on-resistance behavior (right)                                         | 55 |

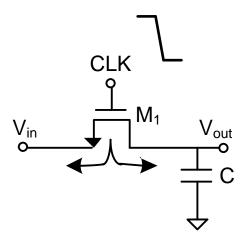

| 3.9  | Charge injection through the source and drain terminals                                       | 56 |

| 3.10 | Clock feedthrough through gate-source and gate-drain overlap capacitance.                     | 57 |

| 3.11 | Dummy switch to reduce the charge injection and clock feed<br>through. $\ \ .$ $\ \ .$        | 58 |

| 3.12 | Block diagram of an N-bit flash ADC                                                           | 60 |

| 3.13 | Two-step ADC architecture                                                                     | 61 |

| 3.14 | Subranging ADC architecture                                                                   | 62 |

| 3.15 | Pipeline ADC architecture                                                                     | 63 |

| 3.16 | Folding ADC architecture                                                                      | 64 |

| 3.17 | Successive approximation ADC architecture (top) and its operation prin-                       |    |

|      | ciple (bottom)                                                                                | 66 |

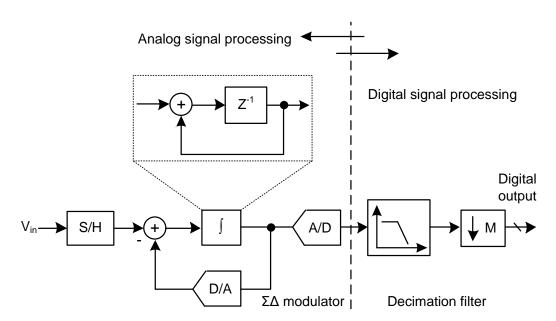

| 3.18 | Sigma-delta ADC architecture                                                                  | 67 |

LIST OF FIGURES ix

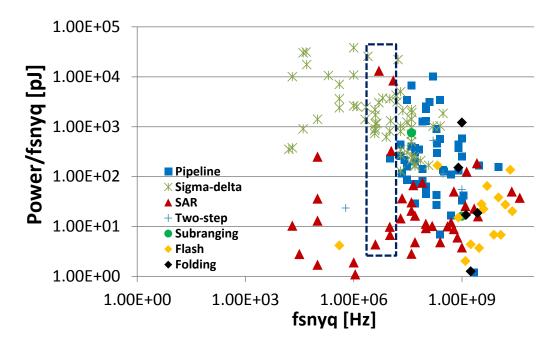

| 3.19 | ADC architecture power efficiency comparison                                  | 68  |

|------|-------------------------------------------------------------------------------|-----|

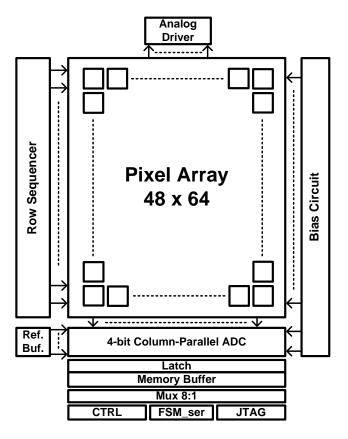

| 4.1  | Global architecture of the CMOS pixel sensor                                  | 76  |

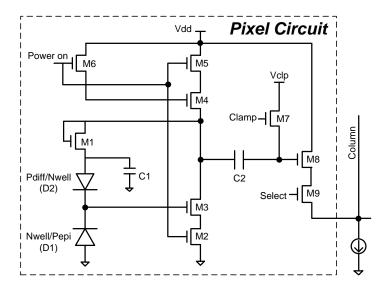

| 4.2  | SB pixel architecture                                                         | 77  |

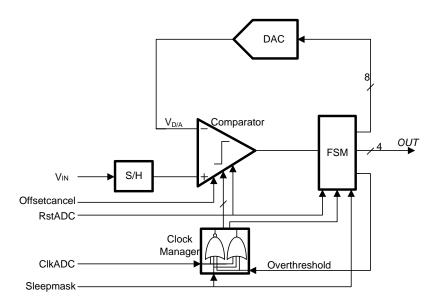

| 4.3  | ADC block diagram                                                             | 79  |

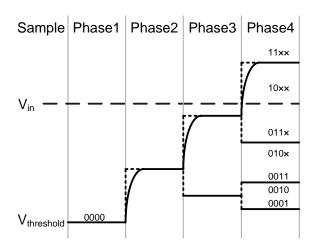

| 4.4  | ADC approximation procedure diagram                                           | 80  |

| 4.5  | Input/output characteristic of an ideal multiple-bit/step ADC                 | 81  |

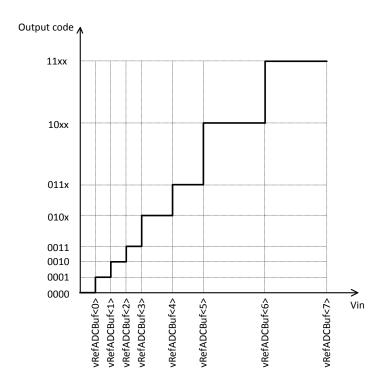

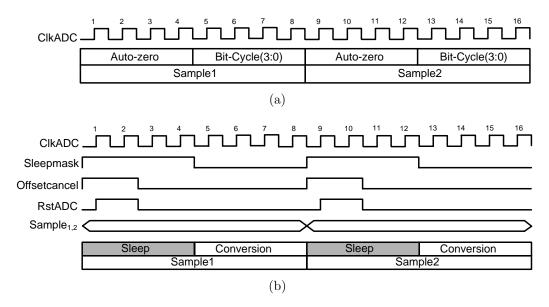

| 4.6  | ADC operation waveforms showing (a) operation plan (b) timing control         | 82  |

| 4.7  | Typical sample-and-hold circuit                                               | 84  |

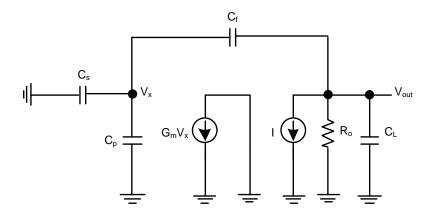

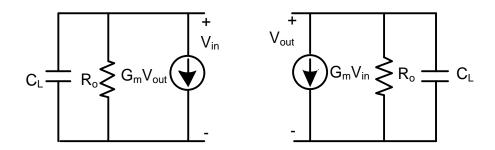

| 4.8  | Small signal model of the switched-capacitor (SC) circuit                     | 84  |

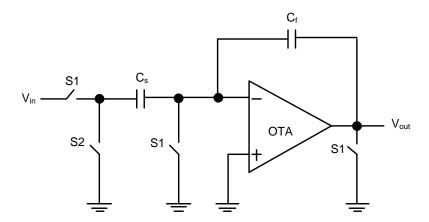

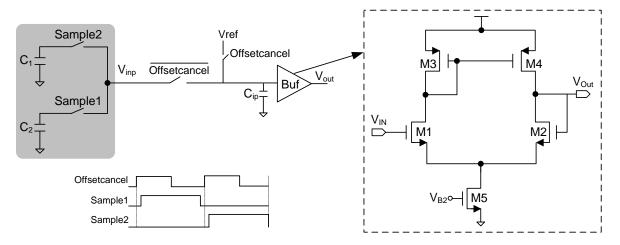

| 4.9  | (a) Sample and hold architecture and (b) related timing diagram               | 87  |

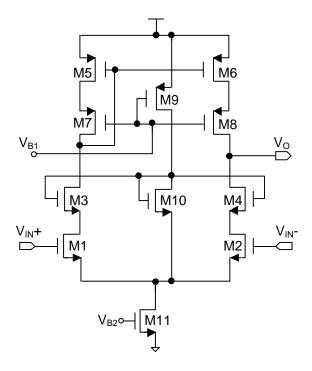

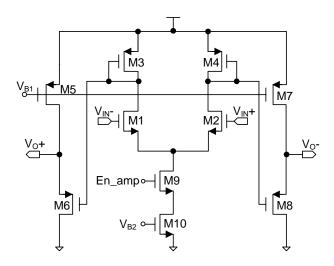

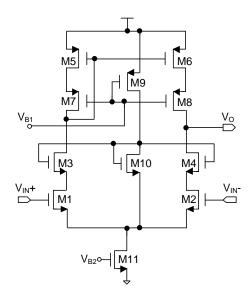

| 4.10 | OTA schematic                                                                 | 89  |

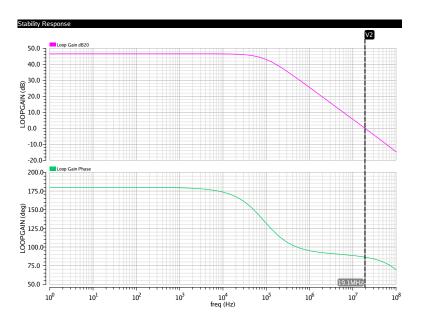

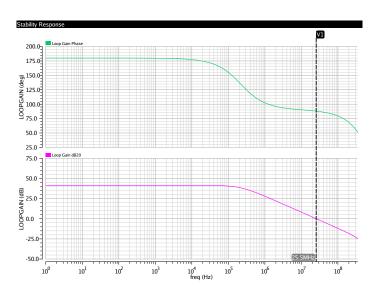

| 4.11 | Loop gain and phase margin of the OTA                                         | 90  |

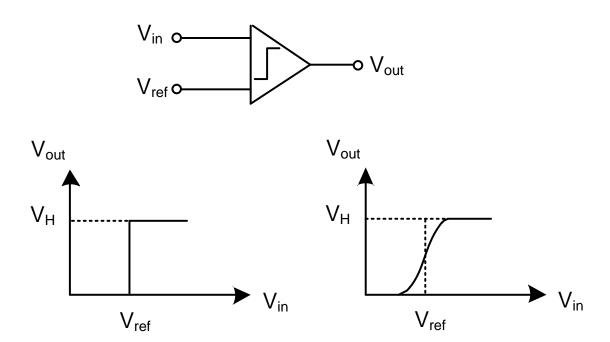

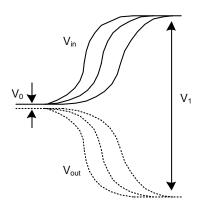

| 4.12 | Input/output characteristic of an ideal comparator and a high-gain amplifier. | 92  |

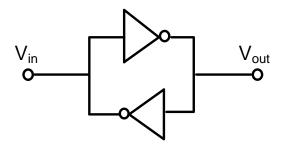

| 4.13 | A simple latch comprising two back-to-back amplifiers                         | 93  |

| 4.14 | A simplified small signal model of the latch                                  | 93  |

| 4.15 | Time response of the latch                                                    | 94  |

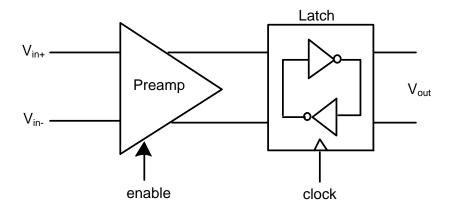

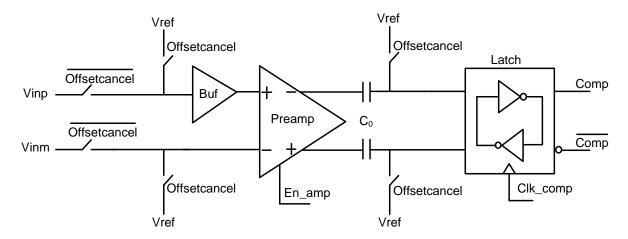

| 4.16 | Offset compensated comparator with preamplifier                               | 95  |

| 4.17 | Auto-zeroed comparator diagram                                                | 96  |

| 4.18 | Circuit diagram with buffer                                                   | 97  |

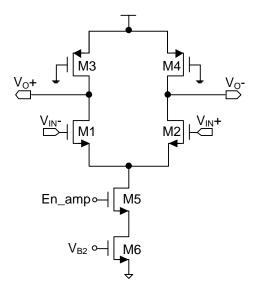

| 4.19 | Switched preamplifier schematic                                               | 97  |

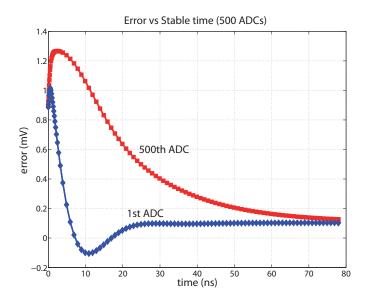

| 4.20 | Dynamic error versus the settling time of the ADC array                       | 98  |

| 4.21 | Dynamic latch with current source                                             | 100 |

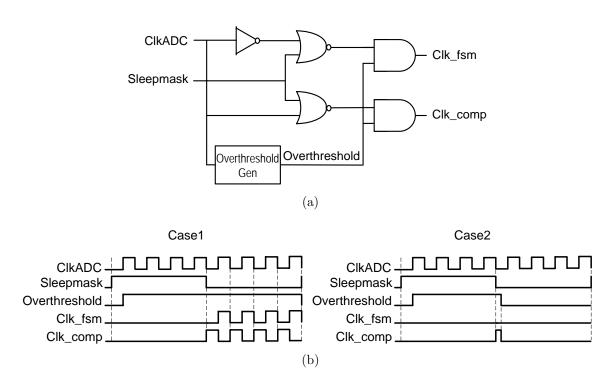

| 4.22 | (a) clock manager and (b) related timing diagram                              | 102 |

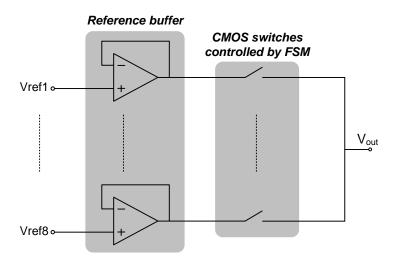

| 4.23 | DAC diagram                                                                   | 103 |

| 4.24 | Simulated DAC (a) output voltage and (b) dynamic error                        | 103 |

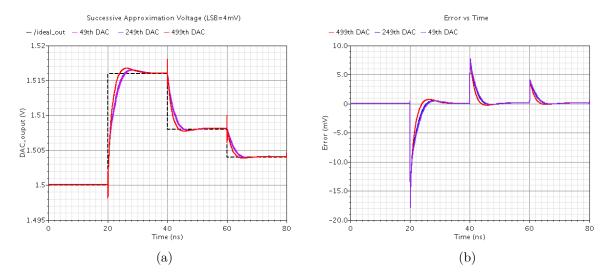

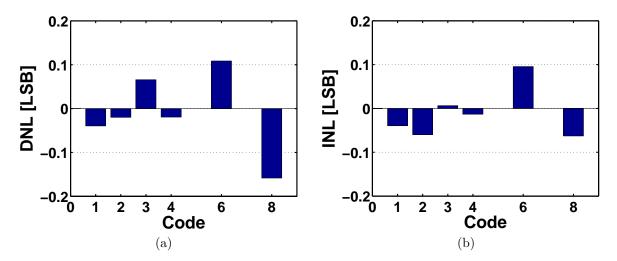

| 4.25 | Simulated (a) DNL and (b) INL versus code                                     | 104 |

| 4.26 | Layout of the sensor prototype                                                | 106 |

| 5.1  | Proximity test board                                                          | 112 |

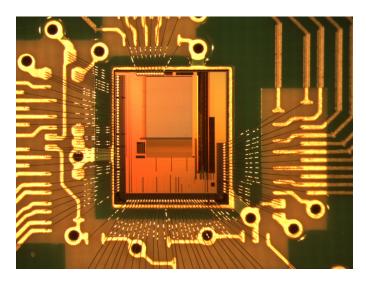

| 5.2  | Microphotograph of wire-bonded chip                                           | 113 |

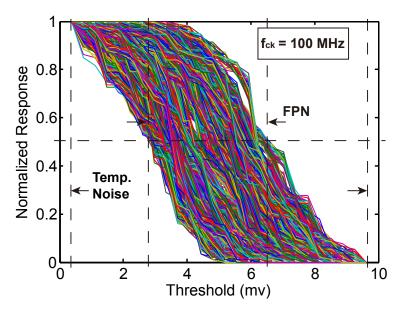

| 5.3  | Normalized response versus threshold voltage                                  | 114 |

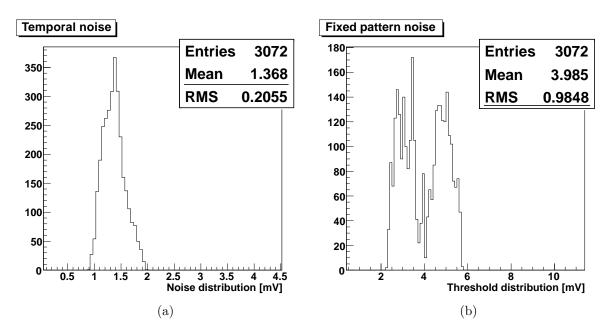

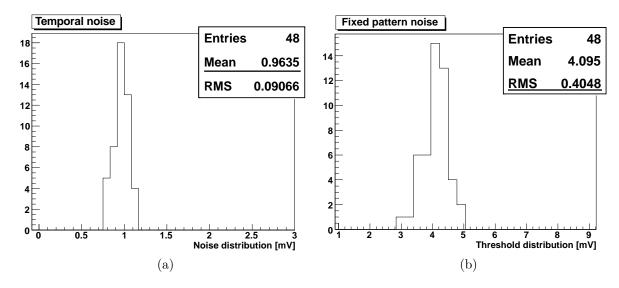

| 5.4  | (a) Measured temporal noise (b) fixed pattern noise                           | 115 |

LIST OF FIGURES

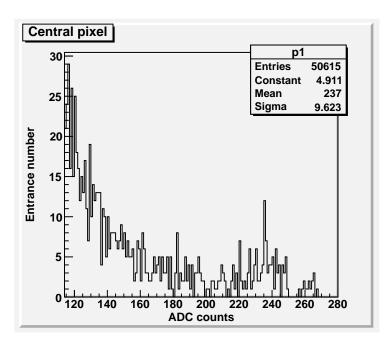

| 5.5  | Calibration results with 5.9 keV X-ray photons for a single pixel. The        |   |

|------|-------------------------------------------------------------------------------|---|

|      | tested pixel is with a standard epitaxial layer                               | ŝ |

| 5.6  | Total charge collection with 5.9 keV X-ray photons for different clusters.    |   |

|      | The test is performed at room temperature                                     | 7 |

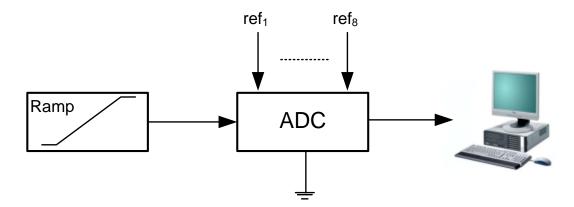

| 5.7  | Test bench of the ADC measurement                                             | 3 |

| 5.8  | Timing diagram of the ADC measurement                                         | 3 |

| 5.9  | Normalized number of counts versus threshold voltage                          | 9 |

| 5.10 | (a) Measured temporal noise and (b) fixed pattern noise                       | 9 |

| 5.11 | Basic histogram test setup                                                    | ) |

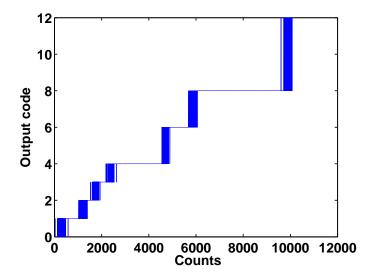

| 5.12 | Number of counts versus ADC output code                                       | ) |

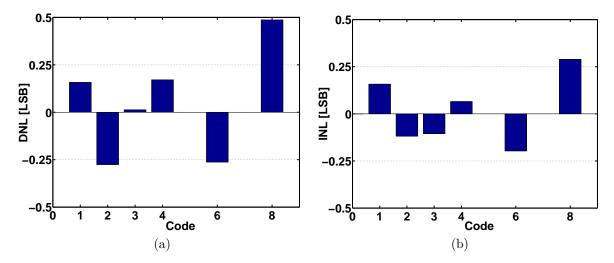

| 5.13 | (a) Measured DNL and (b) INL versus code                                      | 1 |

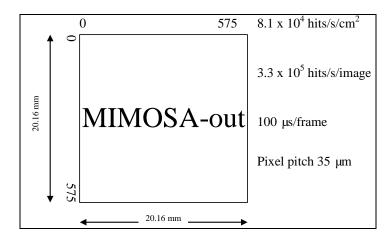

| 6.1  | Characteristics of the full size sensor in the outer layers                   | ദ |

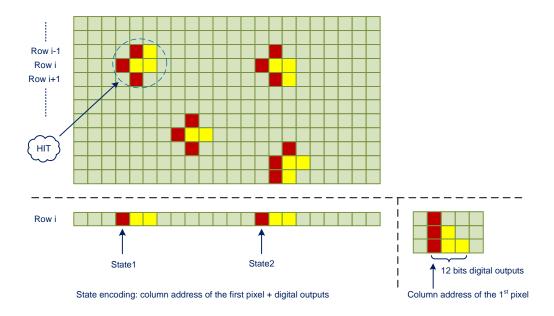

| 6.2  | Schematic of the pixels delivering signal above threshold                     |   |

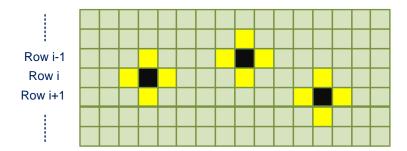

| 6.3  | Concept of a hit represented by a regular cluster                             |   |

| 6.4  | Concept of sparse scan including searching states and identifying hits with   | , |

| 0.1  | a group of three pixels                                                       | 3 |

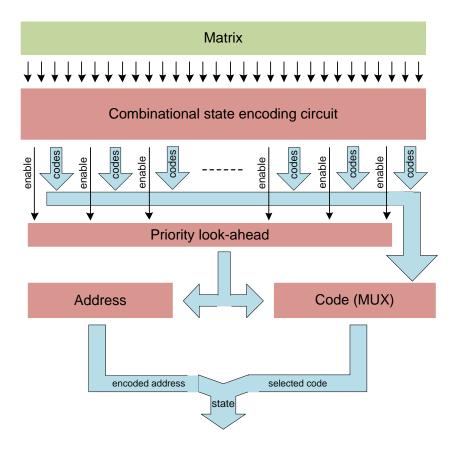

| 6.5  | Block diagram of the state encoding circuit                                   |   |

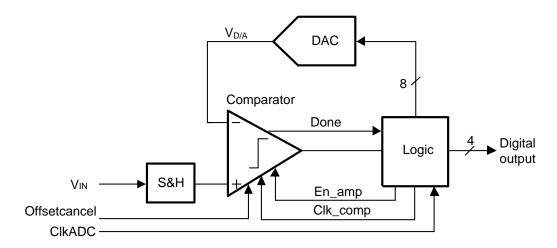

| 6.6  | Improved ADC block diagram                                                    |   |

| 6.7  | (a) Enhanced sample and hold architecture and (b) related timing diagram. 132 |   |

| 6.8  | OTA schematic                                                                 |   |

| 6.9  | Loop gain and phase margin of the OTA                                         |   |

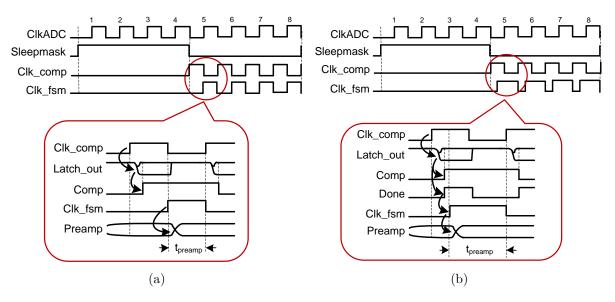

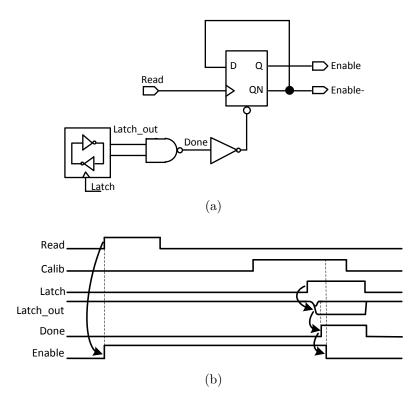

|      | Waveforms showing (a) standard bit-cycling (b) self timed bit-cycling 136     |   |

|      | Self-timed comparator diagram                                                 |   |

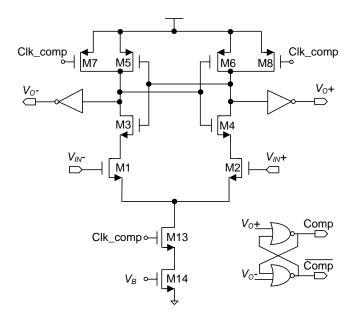

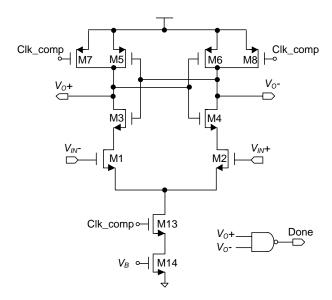

|      | Switched preamplifier schematic                                               |   |

|      | Dynamic latch with current source                                             |   |

|      | Simulated (a) DNL and (b) INL versus code                                     |   |

|      | Schematic of the discriminator                                                |   |

|      | Enabled (a) preamplifier and (b) source follower                              |   |

|      | (a) Enable signal generation and (b) related timing                           |   |

|      |                                                                               |   |

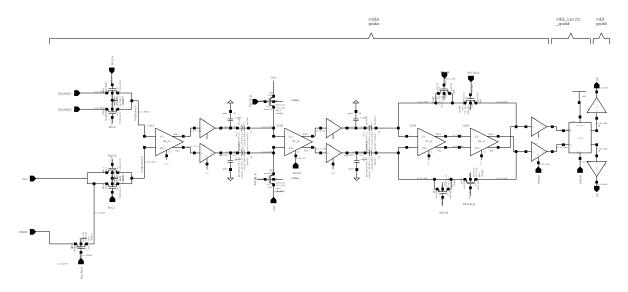

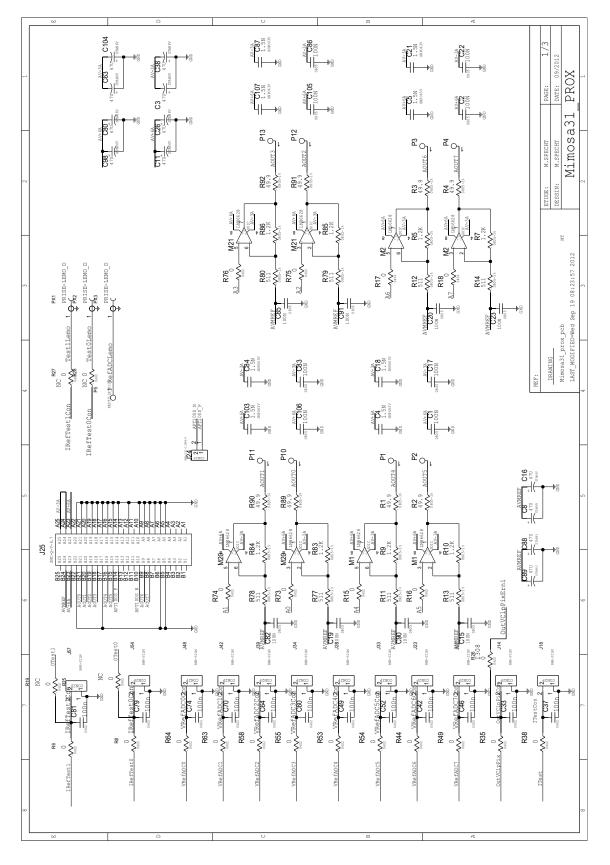

| B.1  | First page of the schematic                                                   |   |

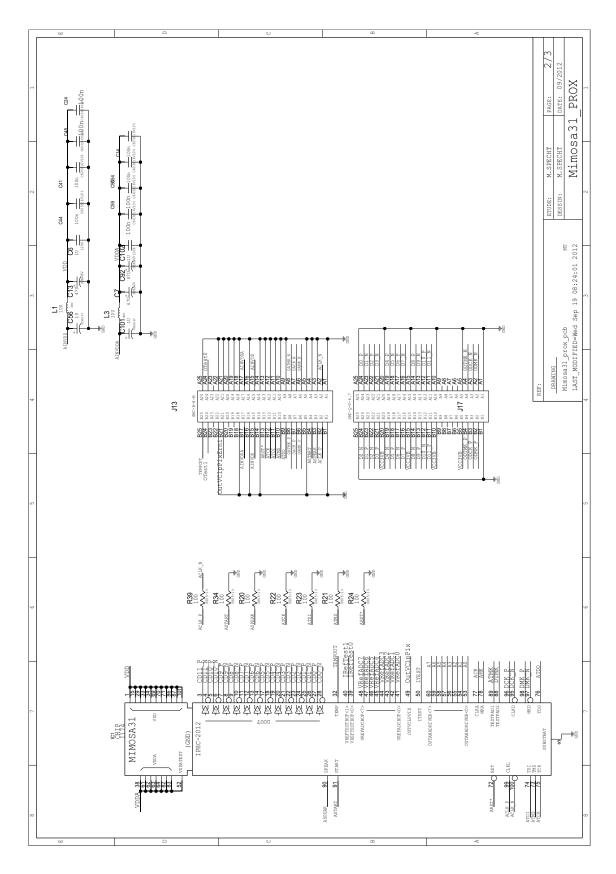

| B.2  | Second page of the schematic                                                  |   |

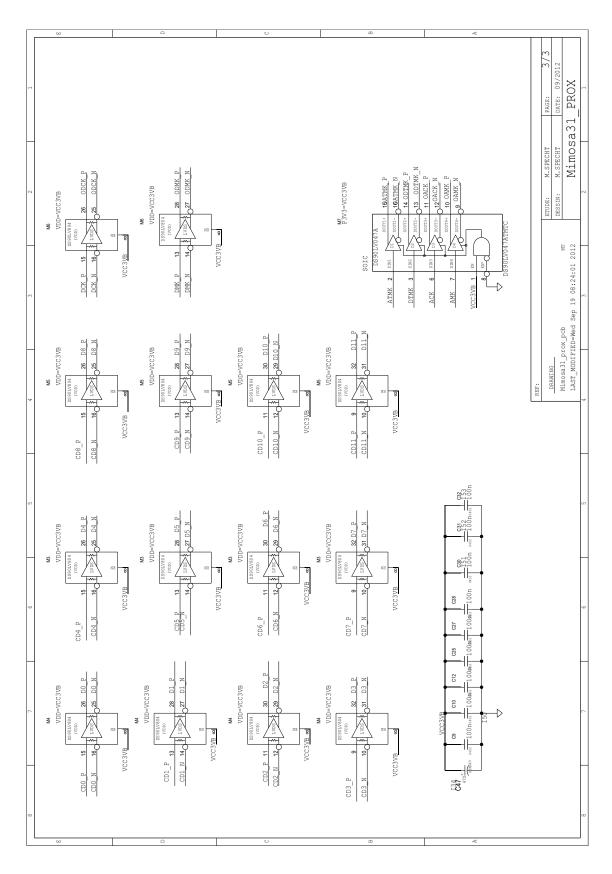

| B.3  | Third page of the schematic                                                   | 3 |

# List of Tables

| 1.1 | Anticipated impact parameter resolution for the ILD, compared to other   |

|-----|--------------------------------------------------------------------------|

|     | collider experiments                                                     |

| 1.2 | Geometrical parameters of the two vertex detector options                |

| 2.1 | Extrapolation from previous measurements. The spatial resolution depends |

|     | on the pixel pitch, epitaxial layer and number of bits                   |

| 4.1 | The simulation results of the pixel circuit                              |

| 4.2 | The simulation results of the OTA                                        |

| 4.3 | The simulation results of the preamplifier                               |

| 4.4 | The simulation results of the dynamic latch                              |

| 4.5 | Performance Summary                                                      |

| 5.1 | Performance Summary of the Sensor Prototype                              |

| 6.1 | The simulation results of the OTA                                        |

| 6.2 | The simulation results of the preamplifier                               |

| 6.3 | Performance summary                                                      |

| A.1 | JTAG instruction registers                                               |

| A.2 | ID code of MIMOSA 31                                                     |

| A.3 | Bias generation register                                                 |

| A.4 | Pattern line register                                                    |

| A.5 | Disable ADC register                                                     |

| A.6 | Pixel sequencer configuration                                            |

| Α 7 | ADC sequencer configuration 154                                          |

### Abstract

This work deals with the design of a CMOS pixel sensor prototype (called MIMOSA 31) for the outer layers of the International Linear Collider (ILC) vertex detector. CMOS pixel sensors (CPS) also called monolithic active pixel sensors (MAPS) have demonstrated attractive performance towards the requirements of the vertex detector of the future linear collider. MIMOSA 31 developed at IPHC-Strasbourg is the first pixel sensor integrated with 4-bit column-level ADC for the outer layers. It is composed of a matrix of 64 rows and 48 columns. The pixel concept combines in-pixel amplification with a correlated double sampling (CDS) operation in order to reduce the temporal and fixed pattern noise (FPN). At the bottom of the pixel array, each column is terminated with an analog to digital converter (ADC). The self-triggered ADC accommodating the pixel readout in a rolling shutter mode completes the conversion by performing a multi-bit/step approximation. The ADC design was optimized for power saving at sampling frequency. Accounting the fact that in the outer layers of the ILC vertex detector, the hit density is in the order of a few per thousand, this ADC works in two modes: active mode and inactive mode. This thesis presents the details of the prototype chip and its laboratory test results.

**Keywords**: CMOS pixel sensors (CPS), monolithic active pixel sensors (MAPS), International Linear Collider (ILC), vertex detector, correlated double sampling (CDS), analog to digital converter (ADC), column-level, self-triggered, multi-bit/step approximation.

# Résumé en Français

### R.1 Introduction

Les expériences de Physique des Hautes Energies, telles que le futur International Linear Collider (ILC), requièrent des détecteurs de vertex de haute précision qui doivent être composés de capteurs à pixels très granulaires et minces. Profitant des conditions de fonctionnement de l'ILC, qui sont beaucoup moins contraignantes que celles du Large Hadron Collider (LHC), des spécifications physiques telles que la résolution spatiale peuvent être privilégiées au détriment de la vitesse de lecture ou de la tolérance aux radiations. Les capteurs CMOS à pixels (CPS), également appelés capteurs monolithiques à pixels actifs (MAPS) et qui sont un axe fort de recherche à l'IPHC-Strasbourg (Institut Pluridisciplinaire Hubert Curien), ont montré des performances intéressantes pour les spécifications du détecteur de vertex. Ils peuvent facilement atteindre la granularité et le budget matière recherché, et ne nécessitent pas la mise en place un système de refroidissement qui augmente le budget matière dans le volume fiduciel du détecteur de vertex.

Le sujet de cette thèse est la conception d'un concevoir un prototype de capteur à pixel CMOS adapté aux couches extérieures du détecteur de vertex ILD VTX. L'ILD VTX impose des exigences strictes sur les capteurs à pixels CMOS. Il existe deux géométries différentes pour le VTX, comme l'illustre la figure 1. L'un d'eux (VTX-SL) dispose de 5 couches simples équidistants, alors qu'une option alternative (VTX-DL) dispose de 3 couches doubles. Les capteurs équipant la couche la plus interne dans les deux géométries doivent avoir une résolution spatiale inférieure à 3  $\mu$ m et associée à un temps d'intégration très court (moins de 50  $\mu$ s) en raison du beamstrahlung. Dans les conditions de fonctionnement de l'ILC, une milliseconde de collisions intenses est entrecoupée de 199 ms sans faisceau. Le bruit de fond du faisceau nécessite que pendant les collisions d'un train de particule, les capteurs doivent être lu vingt fois ou plus afin de maintenir un

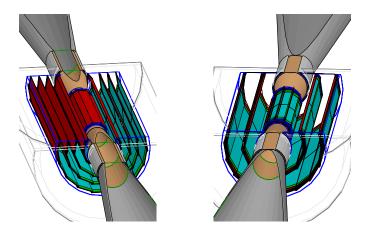

Figure 1: Géométrie d'un détecteur de vertex. A gauche: 5 couches simples (VTX-SL). A droite: 3 couches doubles (VTX-DL).

taux d'occupation de la matrice de pixels inférieur à 1%. Cette contrainte nécessite un effort de R&D se focalisant sur un design à haute vitesse de lecture. Des pixels à faible pitch terminés par un discriminateur est proposé. Les capteurs envisagés pour les couches externes, qui sont les plus grandes, s'étendant sur près de 90% de la surface totale du VTX, ont moins de contraintes en termes de résolution spatiale et de vitesse de lecture. Une résolution spatiale de 3-4  $\mu$ m combinée avec un temps d'intégration inférieur à 100  $\mu$ s devrait constituer un compromis acceptable. Dans ce cas, l'effort de conception se concentre sur la réduction de la consommation d'énergie. Un pixel avec un pitch de 35  $\mu$ m combiné avec un convertisseur analogique-numérique (analog-to-digital converter, ADC) de 4 bits est proposé, réduisant ainsi la consommation d'énergie tout en gardant la résolution spatiale nécessaire.

### R.2 Travail Doctoral

#### R.2.1 Partie 1

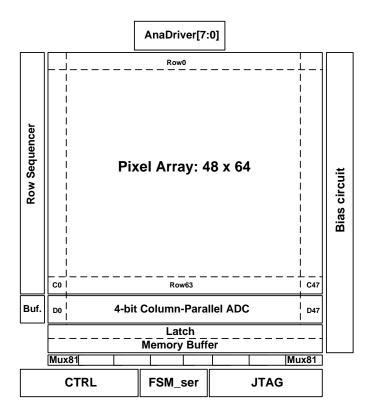

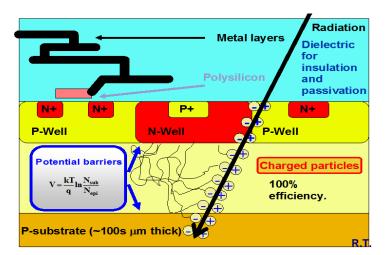

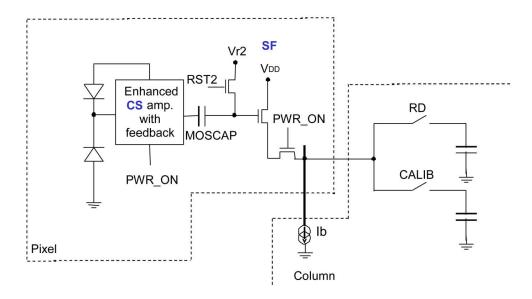

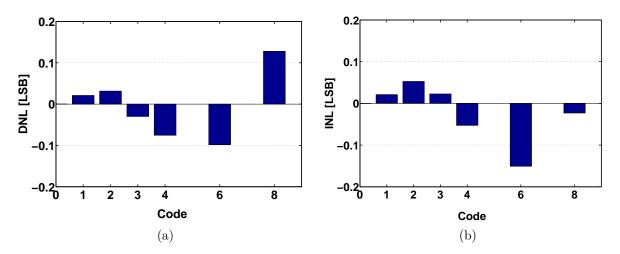

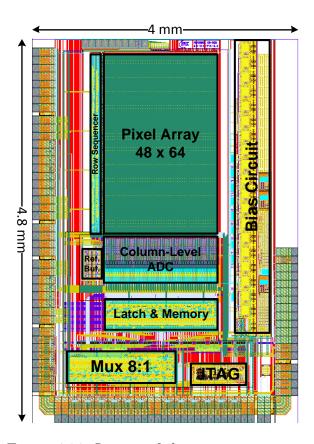

L'architecture du prototype nommé MIMOSA 31 comprend une matrice de pixels de 48 colonnes par 64 lignes, des ADC en bas de colonne et d'un microcircuit de lecture numérique périphérique, comme l'illustre la figure 2.

Les pixels sont lus ligne par ligne en mode d'obturation roulant. Chaque pixel est

Figure 2: Schéma de principe du capteur à pixels CMOS proposé.

composé d'une amplification interne avec une opération de double échantillonnage corrélé (correlated double sampling, CDS), qui a été validé dans les capteurs précédents (MI-MOSA 26 conçu pour le projet EUDET de téléscope de faisceau et ULTIMATE qui équipe le sous-système STAR-PXL). Les ADCs de bas de colonne recoivent la sortie des pixels en parallèle et réalisent la conversion en effectuant une approximation de multi-bit/step défini ci-dessous. L'architecture de l'ADC est similaire à un convertisseur à approximations successives (successive approximation register, SAR), avec une faible consommation d'énergie et une vitesse modérée (plusieurs méga-échantillons par second). Les prototypes précédents ont permis de vérifier que le bruit du pixel est d'environ 1 mV. Afin diminuer la résolution sur la position de reconstruction de la particule, le bit le moins significatif (least significant bit, LSB) est fixé au niveau du bruit du pixel. Des études de physique antérieures montrent que le codage approximatif de l'amplitude des pixels ayant un fort signal dans un cluster ne dégrade pas la résolution spatiale. Par conséquent, un encodage variable du signal est utilisé, allant d'un maximum de 4 bits pour les sig-

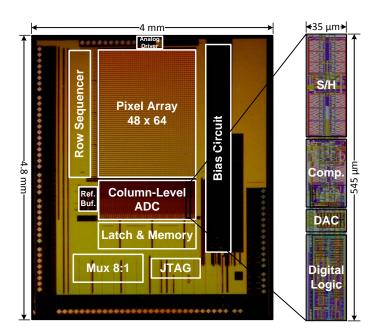

Figure 3: Microphotographie du capteur.

naux de faible amplitude à seulement 2 bits pour les grands signaux. Après la conversion analogique/numérique, les sorties numériques sont mémorisées, et transmises en série vers l'extérieur à travers un multiplexeur de 8 vers 1. Les paramètres de réglage du capteur sont programmables à distance à travers le protocole JTAG. Afin de comparer les performances des circuits de lecture, le circuit possède également huit sorties analogiques.

Sachant que dans les couches externes de l'ILC VTX, la densité de pixels touchés est de l'ordre de quelques pour mille, l'ADC est conçu pour fonctionner en deux modes (actifs et inactifs) afin de minimiser la consommation d'énergie. L'ADC utilise une tension de seuil pour déclencher la conversion. Si le signal du pixel est supérieur au seuil, l'ADC fonctionne en mode actif et effectue la conversion, sinon, l'ADC fonctionne en mode inactif et reste en sommeil jusqu'à la prochaine conversion. L'utilisation de cette méthode permet d'économiser considérablement la puissance consomée.

Le prototype a été conçu et fabriqué dans une technologie CMOS 0.35  $\mu$ m, 2 couches de polysilicium et 4 niveaux de métal. La superficie totale du circuit est de 4 × 4.8 mm<sup>2</sup>, comme l'illustre la figure 3. La matrice de pixels est de 48 × 64 pixels avec un pas de 35  $\mu$ m. La matrice d'ADC en bas de colonnes est situés directement en dessous de la matrice de pixels. La surface d'un ADC est de 35 × 545  $\mu$ m<sup>2</sup>.

Les résultats des tests préliminaires indiquent que MIMOSA 31 répond aux exigences des spécifications de la conception. Les tests en laboratoire ont été effectués en trois parties: le test de la matrice de pixels avec les ADCs, le test des pixels et enfin le test des ADCs. Ces résultats des tests permettent de déterminer les performances de base, y compris le bruit temporel, le bruit motif fixe (fixed pattern noise, FPN), le bruit équivalente en charge (equivalent noise charge, ENC), le facteur de conversion charge-tension (charge-to-voltage conversion factor, CVF), l'efficacité de collection des charges (charge collection efficiency, CCE) et la non-linéarité.

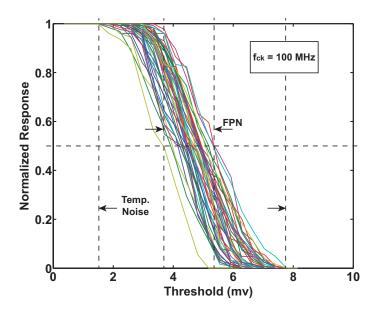

Les courbes de transfert indiquant les performances en bruit, ont été obtenues par balayage de la tension de seuil de l'ADC. A partir de ces courbes ayant une distribution cumulative, on peut déduire le bruit temporel et le FPN. Un bruit temporel de 1.36 mV et un FPN de 0.98 mV ont été mesurés sur l'ensemble pixel et ADC.

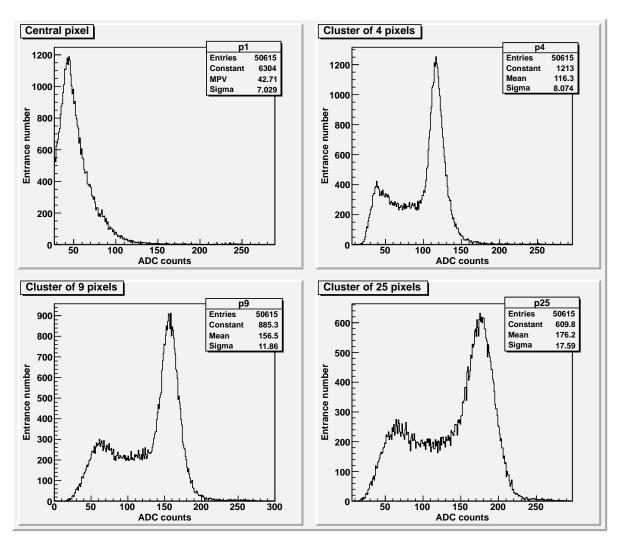

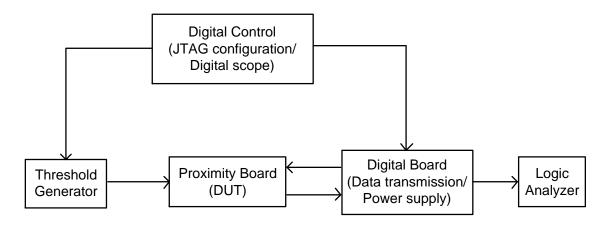

Le test des pixels seuls permet d'extraire un bruit équivalent en charge (ENC) correspondant à  $18.6~{\rm e_{rms}^-}$ . Le facteur de conversion charge-tension mesuré (CVF) obtenu pour un unique pixel est de  $60~\mu{\rm V/e^-}$ . Afin d'étudier la répartition des charges, les performances des groupes de pixels touchés ont été analysées. L'efficacité de la collection des charges (CCE) mesuré sur p1 (pixel central), p4 (2 × 2 pixels), p9 (3 × 3 pixels) et p25 (5 × 5 pixels) sont respectivement de 18%, 49%, 66% et 74%.

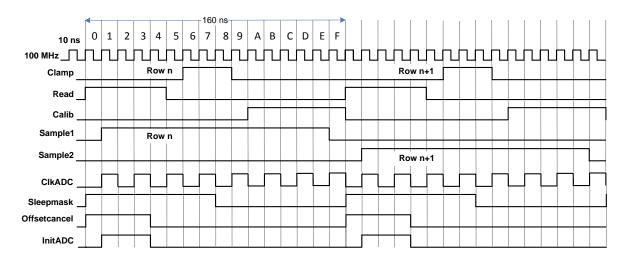

Le test des ADCs seuls a permis d'analyser la non-linéarité. La non-linéarité différentielle mesurée (differential nonlinearity, DNL) est de 0.49/-0.28 LSB et la non-linéarité intégrale (integral nonlinearity, INL) est de 0.29/-0.20 LSB. Le temps de conversion de l'ADC est de 80 ns avec une fréquence d'échantillonnage de 6.25 MHz. Il consomme 486  $\mu$ W en mode inactif, qui est de loin le plus fréquent, cette consomation s'élève à 714  $\mu$ W en mode actif.

### R.2.2 Partie 2

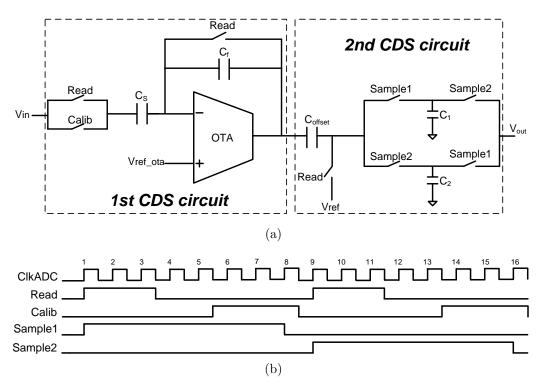

Afin de réduire davantage la consommation d'énergie globale du capteur, une nouvelle architecture auto-synchronisée de l'ADC à très faible puissance est proposée. La structure de cette nouvelle solution consiste en une amélioration de l'échantillonneur-bloqueur (sample-and-hold, S/H) et l'ajout d'une technique d'auto-synchronisation. La partie de S/H est renforcée par l'utilisation d'une architecture à double échantillonnage corrélé (CDS) afin de réduire le bruit de motif fixe (FPN) du pixel et de l'amplificateur opéra-

tionnel. Ceci permet d'éviter l'implémentation d'un condensateur d'auto-zéro supplémentaire, minimisant ainsi la consommation de puissance tout en maintenant la conversion des signaux avec les fréquences souhaitées. L'efficacité du comparateur est améliorée en utilisant des signaux auto-synchronisés, et en relâchant le temps de stabilisation du préamplificateur. Avec améliorations la consommation totale d'énergie est réduite jusqu'à 54% en mode inactif et 40% en mode actif, par rapport à l'ADC implanté dans MIMOSA 31.

### R.3 Conclusion

MIMOSA 31 est le premier prototype de capteur CMOS intégrant un ADC en bas de colonne de 4-bit à une matrice de pixels dédiée aux couches externe d l'ILD-VTX. Les résultats préliminaires indiquent que MIMOSA 31 répond au cahier des charges pour cette couche de capteurs. La caractérisation de MIMOSA 31 sera complétée par des tests en faisceau afin de mesurer la résolution spatiale. Le prototype a été conçu avec les caractéristiques d'un capteur de taille finale c'est-à-dire environ  $2 \times 2 \text{ cm}^2$ , et peut donc être facilement étendu dans des versions futures.

Un nouvel ADC auto synchronisé à puissance très faible est développé. La consommation totale d'énergie est considérablement réduite alors que dans le même temps l'ADC maintient une vitesse de conversion élevée. Les résultats de la simulation démontrent que la puissance consommée est réduite de 53% alors que les paramètres d'origine ont été conservés.

# Introduction

High Energy Physics (HEP) experiments, such as the future International Linear Collider (ILC), have expressed an increasing demand for high precise vertex detectors, to be equipped with very granular and thin pixel sensors. Taking advantage of the ILC running conditions, which are much less demanding than those at the Large Hadron Collider (LHC), physics driven specifications such as spatial resolution can be privileged at the expense of read-out speed or radiation tolerance. Since CMOS Pixel Sensors (CPS), also called Monolithic Active Pixel Sensors (MAPS) are well developed at IPHC-Strasbourg (Institut Pluridisciplinaire Hubert Curien), they have demonstrated attractive performances towards the specifications of the vertex detector. They can easily match the targeted granularity and material budget, and do not introduce a cooling system which adds material budget in the fiducial volume of the vertex detector.

This thesis deals with the design of a CMOS pixel sensor prototype adapted to the ILC vertex detector (VTX) outer layers. The International Large Detector (ILD) is one of the detector concepts proposed for the ILC. The ILD VTX has driven stringent requirements on the CMOS pixel sensors. There are two different geometries for the VTX. One of them (VTX-SL) features 5 equidistant single layers, while an alternative option (VTX-DL) features 3 double layers. Sensors equipping the innermost layer in both geometries should exhibit a single point resolution better than 3  $\mu$ m associated to a very short integration time (less than 10  $\mu$ s) because of the beamstrahlung background. In the ILC running conditions one millisecond of intense collisions is interspaced with 199 ms without beam. The beam background dictates that during the collisions of a single bunch train, sensors are supposed to read out twenty or more times to maintain the pixel occupancy below 1%. This requirement motivates an R&D effort concentrating on a high read-out speed design. A small pixel pitch terminated with a discriminator is proposed. The sensors envisioned for the outer layers, which are the largest ones, standing for about 90% of the

xxii Introduction

total VTX surface, have less constrains in term of spatial resolution and read-out speed. A single point resolution of 3-4  $\mu$ m combined with an integration time shorter than 100  $\mu$ s are expected to constitute a valuable trade-off. In this case, the design effort focuses on minimizing the power consumption. A larger pixel pitch of 35  $\mu$ m combined with a 4-bit ADC is proposed, therefore reducing the power consumption and keeping necessary spatial resolution.

This thesis is organized as follows:

- In chapter 1, the ILC physics programme and the ILD vertex detector will be introduced. In this chapter, the physics motivation is outlined, highlighted by the precision measurements of the Higgs Boson candidate that was recently discovered at the LHC. Then the high precise vertex detector that exhibits excellent performance in terms of flavour tagging and track reconstruction is presented. The CMOS pixel sensors (CPS) proposed to equip the vertex detector is described in the end.

- In Chapter 2, the basic principle of the CMOS pixel sensor equipping the vertex detector will be presented. In this chapter, the design specifications, architecture and characteristic of the CPS will be described. With the state-of-the-art CPS developed, these devices are close to comply with all major requirements for the innermost layer and outer layers. Then a sizeable sensor prototype integrated with 4-bit column-level ADCs aiming to equip the outer layers is proposed.

- In Chapter 3, the column-level ADC suitable for our application will be addressed. In this chapter, the performance parameters of an column-level ADC will be presented. Also different techniques will be described in order to eliminate the non-ideal errors. Different ADC architectures are briefly reviewed, and then the column-level architecture suitable for our application are presented, including its basic building blocks.

- In Chapter 4, the design method of the sensor prototype will be presented. In the first section, the system level design of the prototype chip will be described, and then in the following sections circuit implementations including pixel and ADC will be presented. Also the design requirements and considerations will be described in more detail. Finally, the simulation results and layout of the prototype chip will be provided.

- In Chapter 5, the test results are presented. In this chapter, the test board and measurement setup for the sensor prototype will be described. Then the laboratory

Introduction xxiii

test results will be presented, which have been performed on pixels and column ADCs in order to determine the basic performances including temporal noise, fixed pattern noise (FPN), equivalent noise charge (ENC), charge collection efficiency (CCE), charge-to-voltage conversion factor (CVF) and nonlinearity.

- In Chapter 6, improvements on CMOS pixel sensors will be addressed. In this chapter, a zero-suppression method proposed for the digital outputs in MIMOSA 31 will be described in more detail. In the following sections, optimizations such as power saving techniques for both of ADC and discriminator will be presented.

- The conclusions about the prototype chip will be provided at the end. The chip is the first CMOS sensor prototype integrating 4-bit column-level ADCs for the ILC VTX outer layers. It was designed with the specifications of the full size sensor (about 2 × 2 cm<sup>2</sup>), and therefore can be easily extended in the future. Also the perspectives of the CMOS pixel sensor for vertex detector are presented.

# Chapter 1

# **ILC Vertex Detector**

This initial chapter introduces the background for the ILC physics and detector. First, the physics motivation is outlined, highlighted by the precision measurements of the Higgs Boson candidate that was recently discovered at the LHC. Next, the chapter describes the International Large Detector (ILD), one of the detector concepts at the ILC. It has the ability to achieve an excellent vertexing and tracking in order to reconstruct the secondary vertices and to measure precisely the momenta of tracks. The main topic of this thesis is the ILC vertex detector. With the physical requirements, high precise vertex detector that exhibits excellent performance in terms of flavour tagging and track reconstruction is presented. The chapter ends with a description of the CMOS pixel sensors (CPS) proposed to equip the vertex detector.

## 1.1 The ILC Physics Programme

High Energy Physics (HEP) experiments using particle accelerators convert matter into energy and generate new particles by colliding in order to explore the most elementary structure of the universe. During the next few years, experiments at CERN's Large Hadron Collider (LHC) will have the first direct look at Terascale physics. However, the highly extreme data rate and the not well defined initial state of an event make a very complicated realization in precision measurements. After the discoveries, more precise measurements are needed which can be provided by lepton colliders instead of hadron colliders. The advantage of lepton machine is the well defined initial state of the collision due to the structureless leptons and less severe background level that leads to

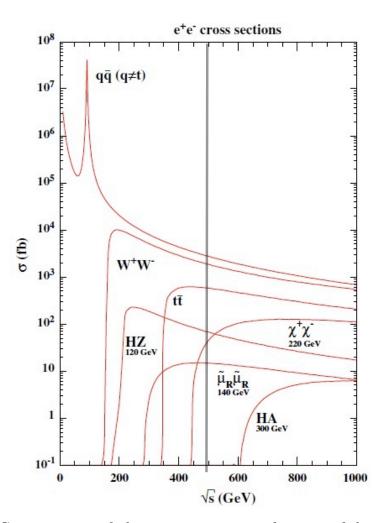

Figure 1.1: Cross sections of physics processes as a function of the collision energy.

clean signatures in the detector frame. The International Linear Collider (ILC) where electrons will collide with positrons is a strong candidate for the precision study of the Higgs boson. It will operate in the center of mass energy range of 250 GeV to 500 GeV, with the possibility for a later upgrade to 1 TeV. The main purpose of the ILC experiment is to measure very precisely the properties of the Higgs particle and any new particles that may exit, following the initial outcome of the LHC experiment.

The ILC programme will access all of the Higgs boson production reactions. Figure 1.1 show the cross sections of physics processes as a function of the collision energy. The Higgs boson programme of the ILC begins at the energy of 250 GeV, near the peak of

the cross section for  $e^+e^- \to Zh$ . The presence of a Z boson at the energy tags the Higgs boson events. This allows direct measurement of the Higgs boson branching ratios. At higher energy, the WW fusion process of Higgs production turns on. Measurement of this process at the full ILC energy of 500 GeV gives a model-independent precision measurement of the Higgs boson. Experiments at 500 GeV also give first measurement of the Higgs boson coupling to  $t\bar{t}$ . At a center of mass energy of 1 TeV, all of the Higgs boson production reactions are fully accessible.

The ILC thus offers a rich experimental programme that addresses the most important open issues in elementary particle physics. In this respect, the ILC will be essential to move forward on mechanism understanding.

### 1.1.1 The ILC Machine

The International Linear Collider (ILC) is a linear particle accelerator, the next generation collider for high energy physics. Compared to the circular collider, the linear collider avoids energy loss caused by synchrotron radiation, allowing to reach high energy. The site for the accelerator has not yet been decided. The total footprint is between 31 km and 50 km, plus two damping rings each with a circumference of 6.7 km. The interaction region of the ILC is designed to host two detectors, which can be moved into the beam position with a "push-pull" scheme. As already well documented in the ILC Reference Design Report (RDR) [1], the ILC programme will extend and complement the physics experiments of the Large Hadron Collider (LHC).

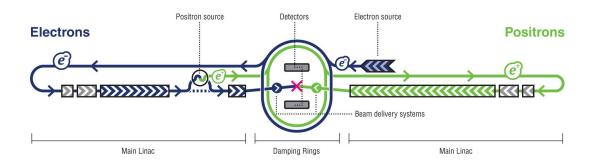

Figure 1.2: Schematic layout of the International Linear Collider.

Figure 1.2 shows a schematic view of the overall layout of the ILC. The electron

source, the damping rings and the positron auxiliary source are centrally located around the interaction region (IR) [2]. The major subsystems include:

- a polarized electron source based on a photocathode DC gun.

- an undulator-based positron source driven by the 150 GeV main electron beam.

- 5 GeV electron and positron damping rings (DR) located in a common tunnel at the center of the ILC complex.

- beam transport from the damping rings to the main linacs, followed by a two-stage bunch compressor system prior to injection into the main linac.

- two 11 km long main linacs (in future will be extended for an upgrade to 1 TeV), utilizing 1.3 GHz SCRF cavities, operating at an average gradient of 31.5 MV/m, with a pulse length of 1.6 ms.

- a 4.5 km long beam delivery system, which bring s the two beams into collision with a 14 mrad crossing angle, at a single interaction point which can be share by two detectors.

ILC has an unprecedented potential for precision measurements, with new windows of exploration for physics beyond the Standard Model. This implies new requirements on experimental accuracies. This in turn drives the need for more precise detectors.

#### 1.1.1.1 Beam Related Background

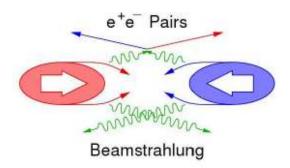

Figure 1.3: Illustration of the pinch effect in bunch collisions.

The ILC may provide a very clean experimental environment compared to hadron colliders, but it is certainly not background-free. The most important source of unwanted interactions are machine induced background. The beam interactions are described as

follows. When the two opposite bunches approach each other, they exert a significant electromagnetic force. The individual particles will be accelerated towards the center of the oncoming bunch, as shown in figure 1.3. This mutual attraction is known as the pinch effect and has both advantages and disadvantages. The pinch effect reduces the size of the colliding bunches, increasing the luminosity by a factor of  $\sim 2$ . On the other hand, the deflection of particles by the charge of the opposite bunch will cause beamstrahlung photons which degrade the energy of the beam. The rate of beamstrahlung pairs create high occupancies that demand fast readouts.

#### 1.1.1.2 Beam Time Structure

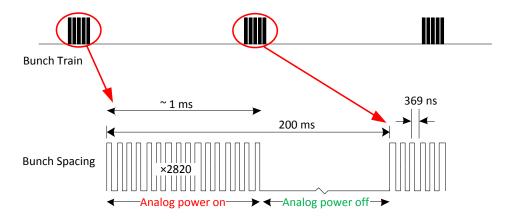

Figure 1.4: Bunch timing scheme of the ILC.

Events at the ILC are accompanied by a beamstralung background. Each crossing produces a large flux of electrons and protons caused by incoherent pair production and bremstasslung in the intense fields at the interaction point. Figure 1.4 shows the beam structure anticipated for the ILC, containing 2820 bunch crossings (BXs), each separated by 369 ns and followed by a bunch gap of 199 ms [3]. The frequency of the bunch trains is 5 Hz. Each bunch trains is about 1 ms, which translates into a machine duty cycle of  $\sim 0.5\%$ .

The low event rate and moderate background allow a variety of strategies to be considered to optimize the vertex detector. The long inter-train gap raised the possibility of detector during the gap, rather than during the train. The low duty factor means that

6 1.2. ILD at ILC

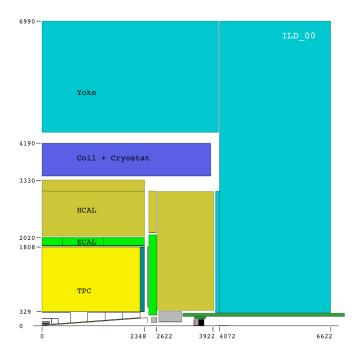

Figure 1.5: Schematic view of the ILD detector concept.

the average power can be reduced by cycling power off the apparatus in between bunch trains, thereby reducing the mass needed for cooling.

### 1.2 ILD at ILC

Even if the effective collision energy at the LHC will be higher than that of the ILC, measurements could be made more accurately at the ILC. Taking advantage of the ILC running conditions, the physics experiments express a great demands on the high performance detectors. This requires an excellent vertexing and tracking system in order to reconstruct the secondary vertices and to measure precisely the momenta of tracks. This objective translates into the necessity of a precise detector compared to the existing state-of-the-art employed for hadron colliders.

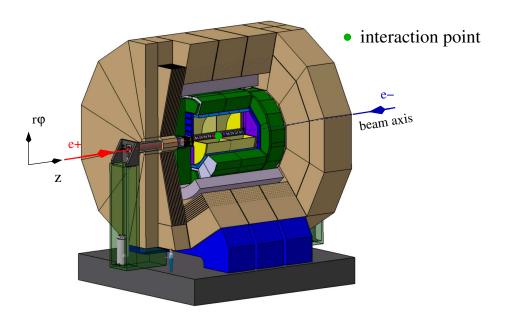

The International Large Detector (ILD) [4] is a concept for a detector at the ILC, as shown in figure 1.5. It is based on the Global Large Detector (GLD) [5] and the Large Detector Comcept (LDC) [6, 7]. ILD combines excellent tracking and finely-grained calorimetry system. This gives ILD the ability to obtain the best possible overall event reconstruction, including the capability to reconstruct individual particles, known as the

Figure 1.6: Quadrant of the ILD detector concept.

Particle Flow approach. The precision that can be achieved by ILD is ideal for studies in particle physics which call for accurate measurements of particles and their properties.

### 1.2.1 The ILD Layout

The ILD concept is designed as a multi-purpose detector. Figure 1.6 shows a schematic view of the quadrant of the ILD detector concept. The proposed ILD detector has the following components.

#### 1.2.1.1 Vertexing

A Si-pixel based vertex detector (VTX) located at the outside of the beam pipe. It is complemented by a silicon tracking system which is constituted by the Silicon Inner Tracker (SIT) in the barrel and the Forward Tracking Disks (FTD) at the endcaps. The VTX detector will consist of multiple layers of state-of-art silicon pixel sensors, with a purely barrel geometry. It is optimized for excellent performance in terms of flavour tagging,

8 1.3. Vertex Detector

long lived particles such as b- and c-hadrons identification and track reconstruction. The main subject of this thesis is the VTX and more details are described in section 1.3.

#### 1.2.1.2 Tracking

The tracking reconstruction is composed of three subdetectors. The main tracker is a large volume time projection chamber (TPC), which plays an important role in the tracking abilities. It is crucial for the reconstruction of the low momentum tracks and the Forward Tracking Disks (FTD) that provide shallow angle coverage. Additional high precision spatial measurements detectors for tracking reconstruction are Silicon Inner Tracker (SIT), Silicon External Tracker (SET) and Endcap Tracking Detector (ETD). The development of the tracking system was driven by the requirement to offer an overall momentum resolution of  $\delta(1/p_T) \simeq 2 \times 10^{-5}/GeV/c$ .

### 1.2.1.3 Calorimetry

The physics program of the ILD requires a jet energy resolution of  $\Delta E_{Jet}/E_{Jet} \sim 3.5\%$ . This target translates into the necessity of high precise calorimetric system. The calorimeters, composed of Electromagnetic Calorimeter (ECAL) and Hadronic Calorimeter (HCAL) are located inside the coil, in order to optimize the jet energy resolution. The ECAL will be a sampling calorimeter using tungsten as an absorber while the HCAL uses stainless steel.

#### 1.2.1.4 Magnetic Field and Yoke

The ILD is designed to operate in a nominal magnetic field of 3.5 Tesla. The main magnetic field is generated by a large volume superconducting coil surrounding the calorimeters. The coil is surrounded by an iron yoke, which returns the magnetic flux. At the same time, the iron is instrumented and serves as a muon detector.

### 1.3 Vertex Detector

To unravel the underlying physics mechanisms of newly observed processes, the identification of heavy flavours will play a critical role. The Vertex Detector (VTX) is the key tool to achieve very high performance flavour tagging by reconstructing displaced vertices [4].

1. ILC Vertex Detector 9

It also plays an important role in the track reconstruction, especially for low momentum particles which don't reach the main tracker or barely penetrate its sensitive volume.

The vertex detector requirements are mainly driven by two competing sources of constraints: the physics goals and the running conditions. The ILC physics goals dictate an unprecedented spatial tree-dimensional point resolution and a very low material budget. The running conditions at the ILC impose the readout speed and radiation tolerance. The requirements are normally in contradiction. High granularity and fast readout compete with each other and tend to increase the power dissipation. Increased power dissipation in turn leads to an increased material budget. The challenges on the vertex detector are considerable and significant R&D is being carried out on both the development of the sensors and the mechanical support.

### 1.3.1 Requirements

In order to identify the flavor (b or charm) of heavy-flavor jets, measure the associated vertex charge and recognize tau-lepton decays, the VTX needs to be optimized in single point resolution. The high granularity necessary to achieve the single point resolution needs to be complemented with a particularly low material budget allowing high precision pointing with low momentum tracks.

The impact parameter resolution from the vertex detector is expressed by the usual gaussian expression:

$$\sigma_{ip} = a \oplus b/p \cdot \sin^{3/2}(\theta) \tag{1.1}$$

where p and  $\theta$  are the particle momentum and polar angle respectively. The parameters a and b can be given by:

$$a = \sigma_{s.p.} \frac{R_{int} \oplus R_{ext}}{R_{ext} - R_{int}} \tag{1.2}$$

$$b = R_{int} \cdot 13.6 MeV/c \cdot z \cdot \sqrt{\frac{x}{X_0 sin\theta}} \left[ 1 + 0.038 \cdot ln(\frac{x}{X_0 sin\theta}) \right]$$

(1.3)

where  $\sigma_{s.p.}$  is the spatial resolution of the sensors, z is charge of the impinging particle,  $\frac{x}{X_0 sin\theta}$  is the material crossed by the particle given in radiation length,  $R_{int}$  and  $R_{ext}$  are the inner and outer layers radii respectively.

From equation 1.2, the parameter a depends on the single point resolution  $\sigma_{s.p.}$  and the level arm, which is equal to  $R_{ext} - R_{int}$ . From equation 1.3, the parameter b depends

1.3. Vertex Detector

on the distance of the innermost layer to the IP and the material budget  $(x/X_0)$ . The ILD collaboration has set the targeted values for parameters a  $\leq 5 \ \mu m$  and b  $\leq 10 \ \mu m \cdot GeV/c$ . The values of a and b significantly exceed those achieved so far, as illustrated by the comparison in table 1.1, which compares with vertex detector operated at LEP, SLC and LHC as well as planned at RHIC.

| Accelerator | a (μm) | b $(\mu m \cdot GeV/c)$ |  |

|-------------|--------|-------------------------|--|

| LEP         | 25     | 70                      |  |

| SLC         | 8      | 33                      |  |

| LHC         | 12     | 70                      |  |

| RHIC-II     | 13     | 19                      |  |

| ILD         | < 5    | < 10                    |  |

Table 1.1: Anticipated impact parameter resolution for the ILD, compared to other collider experiments.

Studies show that these specifications are met with the a single point accuracy of  $\lesssim$  3  $\mu m$  for a first measured point of tracks at  $\sim$  15 mm from the IP. The material budget between the Interaction Point (IP) and the first measured point should not exceed a few per mill of radiation length, which translates into an upper bound on the ladder material budget in the order of 0.2%  $X_0$ .

#### 1.3.2 Geometries

The ILD vertex detector has been optimized for high spatial resolution and low material budget. The high granularity, combined with the very powerful track reconstruction capabilities of the other tracking detectors, allows integrating over several bunch-crossings without deteriorating the flavour tagging performance. It is made of 5 or 6 cylindrical layers, all equipped with  $\lesssim 50~\mu \mathrm{m}$  thin pixel sensors. The innermost layer has a radius of 15 - 16 mm, a value for which the beamrelated background rate is expected to still be acceptable. And therefore the innermost layer intercepts all particles produced with a polar angle  $(\theta)$  that  $|\cos\theta| \lesssim 0.97$ .

Figure 1.7 shows the view of the vertex detector geometry. Its geometry appears in two alternative options. One of them (called VTX-SL) consists of 5 equidistant single-

1. ILC Vertex Detector 11

Figure 1.7: Vertex detector geometries. Left: 5 single-sided ladders (VTX-SL). Right: 3 double-sided ladders (VTX-DL).

| geometry | radius[mm] |           | ladder length [mm] |        |  |

|----------|------------|-----------|--------------------|--------|--|

|          | VTX-SL     | VTX-DL    | VTX-SL             | VTX-DL |  |

| Layer 1  | 15.0       | 16.0/18.0 | 125.0              | 125.0  |  |

| Layer 2  | 26.0       | 37.0/39.0 | 250.0              | 250.0  |  |

| Layer 3  | 37.0       | 58.0/60.0 | 250.0              | 250.0  |  |

| Layer 4  | 48.0       |           | 250.0              |        |  |

| Layer 5  | 60.0       |           | 250.0              |        |  |

Table 1.2: Geometrical parameters of the two vertex detector options.

sided ladders (i.e. equipped with one layer of sensors), while the other (called VTX-DL) features 3 double-sided ladders (i.e. each ladder being equipped with two layers of sensors on both faces). Fore both geometries, the sensitive area of the innermost layer is 12.5 cm long while it is 25.0 cm long in the other layers (a priori based on 2, 12.5 cm long, butted ladders). The two sides of the double-sided ladders are about 2 mm apart.

Both conceptual designs meet the ILC goals for impact parameter resolution, with the double ladder option giving an impact parameter resolution which is better, particularly for high momentum tracks. Some of their main geometrical parameters are summarised in table 1.2. The complete VTX-SL ladder thickness is equivalent to 0.11%  $X_0$ , while the

1.3. Vertex Detector

double ladders of VTX-DL represent 0.16%  $X_0$ . These values assume 50  $\mu$ m thin silicon pixel sensors.

#### 1.3.3 Sensor Technologies

The physics goals and running conditions call for sensor technology that offers a high granularity, low material budget and high read out speed. A wide variety of options for the sensor technology are investigated. The technologies presently concentrating most of the R&D effort are charge coupled devices (CCD) [8, 9], Hybrid pixel detectors (HPD), DEPFETs [10, 11] and CMOS Pixel Sensors (CPS) [12, 13].

The charge couple devices are widely used in imaging devices, especially in consumer electronics. They were successfully used as vertex detectors in SLD with very high granularity. The high granularity makes CCD a very attractive solution for tracking devices. However, the readout time is limited by the slow charge transfer. Also another limitation of CCD used as tracking devices is their low radiation tolerance.

Hybrid pixel detectors are built from two separately processed silicon layers. The sensing element and readout electronics are connected together using the flip-chip and bump-bonding techniques. They can offer highly readout speed with the independent electronics. However, they exhibit a series of disadvantages such as limited granularity, large material and high power consumption.

The DEPFET device provides low noise performance and low power dissipation. However, the readout electronics use specialized external VLSI circuits that increase the complexity of the system design. A sizeable size DEPFET detector with a fast readout and low noise performance still needs to be demonstrated.

CMOS pixel sensors (CPS) are fabricated in standard CMOS<sup>1</sup> process, featuring several advantages such as low cost, low power, high speed and high integrity. Recently, CPS are making steady progress towards the specifications of the ILD vertex detector, which have shown that they are close to comply with all major requirements [14], in particular the read-out speed needed to cope with the beam related background. They are considered a strong candidate for the ILD vertex detector. In the following section, we are going to focus on the CMOS pixel sensor technology.

<sup>&</sup>lt;sup>1</sup>standing for Complementary Metal-Oxide-Semiconductor.

#### 1.3.4 CMOS Pixel Sensors for VTX

The CMOS Pixel Sensors (CPS) also called Monolithic Active Pixel Sensors (MAPS) used for charged particle detection are developed at IPHC-Strasbourg [15] since the late nineties. Since earlier in 1990s, these devices were progressively replacing Charge Coupled Devices (CCD) in commercial cameras. Initially these devices could not be straightly used in particle tracking because of their low fill factor, which was in the range of 20-30% caused by in-pixel transistors and metal interconnections. Later the fill factor was increased to nearly 100% by using a barrier at the boundaries of the epitaxial layer. Taking this advantage, CPS have been introduced for particle detection which depart from the commercial visible light imagers, which were too slow, exhibited poor detection efficiency and were radiation soft.

Since the start of the development pioneered at IPHC, most of the R&D effort is invested in the sensor design, including both the detection system and integrated signal processing micro-circuits, and into the characterization of sensor prototypes. In the last 12 years, more than 30 different MIMOSA<sup>1</sup> prototypes have been designed and fabricated. The sensors are manufactured by the CMOS industry and can be thinned down to  $\lesssim 50~\mu m$ . The sensor R&D incorporates radiation tolerance and power dissipation constraints. The CMOS pixel sensors have demonstrated good performances for Minimum Ionizing Particles (MIPS) detection [16, 17]. They have an attractive balance between granularity, material budget, readout speed, radiation tolerance and power dissipation. They make it possible to integrated both the sensing elements and readout electronics on a single substrate, thus creating a detector-on-a-chip.

The ILD VTX has driven stringent requirements on the CMOS pixel sensors. Sensors placed on the innermost layer in both geometries should exhibit a spatial resolution better than 3  $\mu$ m associated to a very short integration time (less than 10  $\mu$ s) due to the beamstrahlung background. This requirement motivates an effort concentrating on a high read-out speed design. The sensors envisioned for the outer layers, which are the largest ones, standing for about 90% of the total VTX surface, have less constrains in term of spatial resolution and read-out speed. A single point resolution of 3-4  $\mu$ m combined with an integration time shorter than 100  $\mu$ s are expected to constitute a valuable trade-off. In this case, the design effort focuses on minimizing the power consumption. This thesis

<sup>&</sup>lt;sup>1</sup>standing for Minimum Ionizing particle MOS Active pixel sensor.

1.4. Summary

focuses on the design of a CMOS pixel sensor prototype suited to the outer layers of ILD vertex detector.

### 1.4 Summary

The ILC physics programme are reviewed in this chapter and the ILD vertex detector is presented which is the main subject of this thesis. Several sensor technologies are compared and CMOS pixel sensors for the vertex detector emerged to take up the challenge of such a high performance vertexing, which calls for high granular and thin sensors. Moreover, they are rather swift and radiation tolerant. In the next chapter, more detail of CPS for charged particle detection will be described.

### **Bibliography**

[1] A. Djouadi, J. Lykken, K. Mönig, Y. Okada, M. Oreglia, and S. Yamashita, "International linear collider reference design report volume 2: physics at the ILC." Aug. 2007. [Online]. Available: http://www.linearcollider.org

- [2] N. Phinney, N. Toge, and N. Walker, "International linear collider reference design report volume 3: accelerator." Aug. 2007. [Online]. Available: http://www.linearcollider.org

- [3] M. A. Thomson, "Detectors at a future linear collider," Birmingham HEP Seminar, Feb. 2011.

- [4] "International large detector letter of intent," The ILD Concept Group, Feb. 2010. [Online]. Available: http://www.ilcild.org

- [5] "GLD detector outline document," GLD Concept Study Group, Jul. 2006. [Online]. Available: http://ilcphys.kek.jp/gld

- [6] "Detector outline document for the large detector concept," LDC Working Group, Jul. 2006.

- [7] T. Behnke, "The LDC detector concept," *Pramana*, vol. 69, no. 5, pp. 697–702, Nov. 2007.

- [8] A. Miyamoto, K. Nakayoshi, Y. Sugimoto, H. Ikeda, T. Nagamine, Y. Takubo, H. Yamamoto, and K. Abe, "FPCCD vertex detector R&D for ILC," Internal Note, Oct. 2007.

- [9] Y. Sugimoto, H. Ikeda, A. Miyamoto, T. Nagamine, Y. Takubo, and H. Yamamoto, "R&D status of FPCCD VTX," presented at the International Linear Collider Workshop 2008, Chicago, USA, Nov. 2008.

- [10] C. Damerell, "ILC vertex detector R&D report of review committee," ALCPG Workshop, Oct. 2007.

- [11] "DEPFET pixel vertex detector for the ILC," Internal Note, DEPFET Collaboration, Oct. 2007.

[12] M. Winter, "Development of swift and slim CMOS sensors for a vertex detector at the international linear collider," ILC Vetex Detector Review, Oct. 2007. [Online]. Available: http://iphc.in2p3.fr/Others.116.html

- [13] M. Winter, J. Baudot, A. Besson, C. Colledani, Y. Degerli, R. De Masi, A. Dorokhov, G. Dozière, W. Dulinski, M. Gélin, F. Guillox, A. Himmi, C. Hu-guo, F. Morel, F. Orsini, I. Valin, and G. Voutsinas, "MIP detection performances of a 100  $\mu$ s readout CMOS pixel sensor with digitised ouputs," presented at the International Linear Collider Workshop 2008, Chicago, USA, Nov. 2008.

- [14] M. Winter, "Development of swift, high resolution, pixel sensor systems for a high precision vertex detector suited to the ILC running conditions," DESY PRC report, Oct. 2009. [Online]. Available: http://iphc.in2p3.fr/Others.116.html

- [15] R. Turchetta, J. D. Berst, B. Casadei, G. Claus, C. Colledani, W. Dulinski, Y. Hu, D. Husson, J. P. Le Normand, J. L. Riester, G. Deptuch, U. Goerlach, S. Higueret, and M. Winter, "A monolithic active pixel sensor for charged particle tracking and imaging using standard VLSI CMOS technology," Nucl. Instr. and Meth. Phys. Res. A, vol. 458, pp. 677–689, Feb. 2001.

- [16] M. Winter, "Achievements and perspectives of CMOS pixel sensors for charged particle tracking," *Nucl. Instr. and Meth. Phys. Res. A*, vol. 623, pp. 192–194, Nov. 2010.

- [17] M. Winter, J. Baudot, A. Besson, G. Claus, A. Dorokhov, M. Goffe, Ch.Hu-Guo, F. Morel, I. Valin, G. Voutsinas, and L. Zhang, "Development of CMOS pixel sensors fully adapted to the ILD vertex detector requirements," presented at the International Workshop on Future Linear Colliders (LCWS'11), Granada, Spain, Sep. 2011.

## Chapter 2

# CMOS Pixel Sensors for Charged Particle Detection

CMOS Pixel Sensors (CPS) have been making steady progress towards the specifications of the ILD vertex detector. They have an attractive balance between granularity, material budget, readout speed, radiation tolerance and power dissipation. In this chapter, the operation principle, the architecture and characteristic of the CPS will be presented. Also the CPS design specifications for the vertex detector are described.

### 2.1 Detection Principle

CMOS pixel sensors have been proposed as an alternative option to CCD devices in image sensor since the early in 1990s. They are designed and fabricated in a standard CMOS technology. Usually there are two types of CMOS sensors: Passive Pixel Sensor (PPS) and Active Pixel Sensor (APS). In the former, only a photodiode is integrated in a pixel with selection switches and then directly connected to the readout circuit. However in the latter, there is an amplifier employed in each pixel to buffer the signals to the output. In this way the CMOS sensor can get better performances such as high signal-to-noise ratio (SNR), high readout speed and good scalability.

The use of CMOS pixel sensors (CPS) for charged particle tracking in subatomic physics emerged to take up the challenge of such a high performance vertexing, which calls for high granular and thin sensors providing  $\sim 100\%$  detection efficiency. Moreover, they are rather swift and radiation tolerant. In a CMOS sensor, the detector is integrated

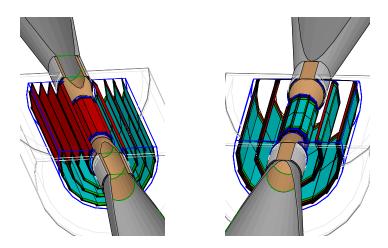

Figure 2.1: CMOS sensor operation principle.

on a substrate through the standard industrial process. The essential aspect for sensors is the high doping, which realizes a sizable thickness of the depleted zone of a reversed biased diode [1]. Figure 2.1 shows the operation principle of the CMOS pixel sensor. The in-pixel transistors are integrated in the p-well  $(p^+)$ , while the sensing element is a reverse biased p-n diode based on the junction of n-well  $(n^+)$  and p-epitaxial layer. The p-well and  $p^{++}$  substrate generate a reflective barrier because of the different doping. The operation principle is described as follows. When the charged particles travel through the thin, almost undepleted epitaxial layer, they liberate charges. The carriers of the signal charge (electrons) diffuse thermally in the layer and are collected by the sensing diode. The signal will be processed by the in-pixel amplifier and transferred to the signal processing circuits by the source follower.

Because the epitaxial layer doping is a few orders of magnitude smaller than that of p-well and  $p^{++}$  substrate, a potential barrier exists at their boundaries. The built-in voltage is given by the following equation [2]

$$V = \frac{kT}{q} ln \frac{N_{sub}}{N_{epi}}. (2.1)$$

where k is the Boltzmann constant, q is the electron charge, T is the absolute temperature,  $N_{sub}$  and  $N_{epi}$  are the doping of the substrate and the epitaxial layer respectively.

The potential acts like a barrier to the charged carriers (electrons). The electrons lib-

Figure 2.2: A simplified diagram of the CMOS pixel sensor.

erated by the radiation in the epitaxial layer diffuse towards the n-well diode, where most of them are collected. Because of the reflective potential barriers, the whole pixel surface is fully sensitive. Since minimum ionising particle generates typically  $\sim 80$  electron-hole pairs per micrometer in the  $\sim 5$  - 15  $\mu$ m thick epitaxial layer, the signal charge ranges from a few hundreds to  $\sim 1000$  e<sup>-</sup>.

It should be noticed that the detector can be thinned down to a few tens of  $\mu m$  ( $\sim 50$   $\mu m$ ) with the standard CMOS technology, which is close to the epitaxial layer without degrading their mechanical support. This can greatly reduce the material budget. Also the fabrications of the sensor are cheap and the their update is fast.

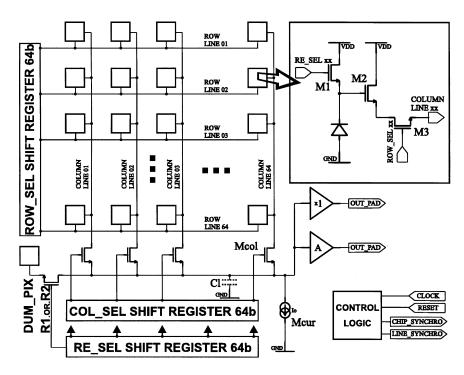

### 2.2 CPS Architecture

CMOS pixel sensor is composed of a pixel array and signal processing micro-circuits. Figure 2.2 shows a simple architecture (MIMOSA-1) of the CMOS pixel sensor. In this simplest version, each pixel is equipped with three transistors: the transistor  $M_1$  for

resetting the sensing diode voltage, the transistor  $M_2$  connected to a source follower which transfers the voltage to the outside and the transistor  $M_3$  for addressing the pixel for the read-out and signal transfer. This architecture does not include any signal processing. In later versions, as described in section 2.2.1, each pixel is implemented with an in-pixel amplification for mitigating the noise sources of the signal, and a correlated double sampling operation for subtracting the average pixel noise.

The readout of the pixel array is achieved with addressing logic and amplifier. The addressing of the pixels is done with two shifters located on the left side and bottom of the matrix. The signal is transferred to the central amplifier through a source follower. Currently an integrated micro-circuit architecture was developed, where the signals delivered by the sensors are discriminated before being filtered by an integrated zero-suppression logic (see section 2.2.2).

#### 2.2.1 Pixel Circuit

The simplest 3 transistors (3T) pixel structure is shown in figure 2.3. The collected charge is converted into voltage through the parasitic capacitor of the p-n diode. The reset operation is used to compensate the leakage current. In this architecture, the leakage current of the diode discharges the capacitor ( $C_{parasitic}$ ), causing a voltage drop at the node K. Thus it affects the common mode voltage of the source follower, introducing a signal offset which significantly depends on the integration time. In general, this offset is considered as fixed pattern noise (FPN).

An improved design is the self biased (SB) pixel architecture (right of figure 2.3). It uses a forward biased diode while employing a reverse biased diode. In this structure, the node K can be treated as a floating node. When the reverse biased diode collects charge, the voltage of the node K drops. Simultaneously the capacitor ( $C_{parasitic}$ ) is recharged by the forward biased diode, and therefore the voltage can slowly recover with a large time constant. This method compensates the leakage current while providing a constant bias via the high resistive diode.

#### 2.2.1.1 Noise Analysis

In this part, the noise analysis is based on the simple 3T architecture. The noise is composed of fixed pattern noise (FPN) and temporal noise. The fixed pattern noise can

Figure 2.3: Structure of the 3T pixel (left) and self-biased (SB) pixel (right).

be reduced by the correlated double sampling (CDS) technique, as described in following section. Thus the temporal noise has become dominant in the pixel. The noise must be analyzed separately in the three operation phases, i.e. the reset, the integration and the readout.

#### • Noise during reset

The reset transistor  $M_1$  (see left of figure 2.3) is used to remove the accumulated charge and compensate the leakage current. In the real case, the reset operation should be done few times in order to avoid the saturation of the diode. When the reset switch  $M_1$  is closed, the readout switch  $M_3$  is open. Then the parasitic capacitor ( $C_{parasitic}$ ) is charged to almost VDD. In this case the average noise can be calculated by

$$\overline{V_{n,rst}^2} = \frac{kT}{C_d}. (2.2)$$

where  $C_d$  is the total parasitic capacitance at the node K. However in real systems the steady state is not obtained because of the insufficient duration of the reset phase. Therefore the average noise is divided by a factor of 2. The equation 2.2 changes to [3]

$$\overline{V_{n,rst}^2} = \frac{1}{2} \frac{kT}{C_d}.$$

(2.3)

The reset noise is the dominant temporal noise and also can be mitigated by CDS technique.

#### • Noise during integration

The main noise during the integration phase is the shot noise due to the diode leakage current  $i_{leak}$ . At room temperature the mean value of this current is in the order of several fA, and the related noise contribution can be neglected in a large integration time ( $\sim$  a few milliseconds). However, this noise should be taken into account when the integration time increases. Without considering the second order effect the mean square value of the noise during integration time is given by

$$\overline{V_{n,int}^2} = \frac{qi_{leak}}{C_d^2} t_{int}.$$

(2.4)