### ÉCOLE DOCTORALE DE PHYSIQUE ET CHIMIE PHYSIQUE

### Institut Pluridisciplinaire Hubert Curie (IPHC)

### **Tianyang WANG**

soutenue le : 25 Septembre 2015

pour obtenir le grade de : Docteur de l'université de Strasbourg

Discipline: Électronique, Microélectronique, Photonique

Spécialité : Instrumentation et Microélectronique

# Development of CMOS Pixel Sensors for the Inner Tracking System Upgrade of the ALICE Experiment

| THÈSE dirigée par :<br>M. HU Yann                      | Professeur, Université de Strasbourg                                                 |

|--------------------------------------------------------|--------------------------------------------------------------------------------------|

| RAPPORTEURS :<br>M. GARDA Patrick<br>M. BARBERO Marlon | Professeur, Université Pierre et Marie CURIE<br>Professeur, Aix Marseille Université |

| AUTRES MEMBRES DU JURY :                               |                                                                                      |

AUTRES MEMBRES DU JURY : M. WINTER Marc

Directeur de recherche, Institut Pluridisciplinaire Hubert Curie

# Contents

| Li       | st of                  | Figure  | es                                         |   | v    |

|----------|------------------------|---------|--------------------------------------------|---|------|

| Li       | st of                  | Tables  | s                                          |   | xi   |

| A        | cknov                  | wledge  | ements                                     | 3 | xiii |

| R        | ésum                   | é en F  | rançais                                    |   | xv   |

| In       | trod                   | uction  |                                            | X | xiii |

| 1        | The                    | ALIC    | CE-ITS upgrade                             |   | 1    |

|          | 1.1                    | The p   | resent ALICE ITS and its limitations       |   | 2    |

|          |                        | 1.1.1   | Overview of the current ALICE ITS          |   | 3    |

|          |                        | 1.1.2   | The limitations of the current ALICE ITS   |   | 4    |

|          | 1.2                    | The re  | equirements of the ALICE ITS upgrade       |   | 5    |

|          | 1.3                    | Overv   | iew of the new ITS                         |   | 8    |

|          | 1.4                    | Silicon | n detector technologies                    |   | 11   |

|          |                        | 1.4.1   | Microtrip detectors                        |   | 11   |

|          |                        | 1.4.2   | Hybrid pixel detectors                     |   | 13   |

|          |                        | 1.4.3   | CMOS pixel sensors                         |   | 14   |

|          | 1.5                    | Summ    | nary                                       |   | 16   |

| <b>2</b> | $\mathbf{C}\mathbf{M}$ | OS piz  | xel sensors for charged particle detection |   | 17   |

|          | 2.1                    | Intera  | ction of particles with matter             |   | 17   |

|          |                        | 2.1.1   | Charged particles                          |   | 18   |

|          |                        | 2.1.2   | Photons                                    |   | 22   |

|          | 2.2                    | Detect  | tion principle and features of CPS         |   | 24   |

|          | 2.3                    | Radia   | tion damage in silicon detectors           |   | 27   |

|   |      | 2.3.1    | Bulk damage                                                                                                                                      |

|---|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|   |      | 2.3.2    | Surface damage                                                                                                                                   |

|   | 2.4  | Noise    |                                                                                                                                                  |

|   |      | 2.4.1    | Temporal noise                                                                                                                                   |

|   |      | 2.4.2    | Fixed pattern noise                                                                                                                              |

|   |      | 2.4.3    | Correlated double sampling                                                                                                                       |

|   | 2.5  | Read-    | out architecture                                                                                                                                 |

|   | 2.6  | Summ     | ary                                                                                                                                              |

| - |      |          |                                                                                                                                                  |

| 3 |      |          | of-the-art CPS and new developments towards the ALICE                                                                                            |

|   |      | upgra    |                                                                                                                                                  |

|   | 3.1  |          | of-the-art CPS: the ULTIMATE sensor                                                                                                              |

|   |      | 3.1.1    | Architecture overview                                                                                                                            |

|   | 2.2  | 3.1.2    | Performances                                                                                                                                     |

|   | 3.2  |          | ng CPS with a new technology $\dots \dots \dots$ |

|   |      | 3.2.1    | The <i>TowerJazz</i> 0.18 $\mu$ m quadruple well process                                                                                         |

|   |      | 3.2.2    | The first exploration $\dots \dots \dots$        |

|   |      | 3.2.3    | Optimization of the in-pixel amplifier                                                                                                           |

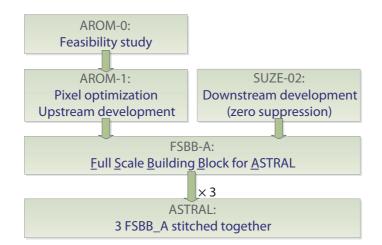

|   | 3.3  |          | Imap to ASTRAL    59                                                                                                                             |

|   | 3.4  | Summ     | ary                                                                                                                                              |

| 4 | Feas | sibility | study: AROM-0 65                                                                                                                                 |

|   | 4.1  | Chip i   | mplementation $\ldots \ldots 65$                      |

|   | 4.2  | Pixel o  | design                                                                                                                                           |

|   |      | 4.2.1    | Pixel pitch                                                                                                                                      |

|   |      | 4.2.2    | Sensing system                                                                                                                                   |

|   |      | 4.2.3    | Discriminator design                                                                                                                             |

|   |      | 4.2.4    | Layout                                                                                                                                           |

|   | 4.3  | Labor    | atory measurement                                                                                                                                |

|   |      | 4.3.1    | Sensing calibration                                                                                                                              |

|   |      | 4.3.2    | Characterization of the full in-pixel circuitry                                                                                                  |

|   |      | 4.3.3    | Characterization of the in-pixel discriminator                                                                                                   |

|   |      | 4.3.4    | Characterization of the latch circuit                                                                                                            |

|   | 4.4  | Summ     | ary                                                                                                                                              |

| <b>5</b> | Fur             | ther p | ixel optimization: AROM-1                                                                 | 103 |  |

|----------|-----------------|--------|-------------------------------------------------------------------------------------------|-----|--|

|          | 5.1             | Lessor | ns learned from AROM-0                                                                    | 103 |  |

|          |                 | 5.1.1  | Pixel V1                                                                                  | 104 |  |

|          |                 | 5.1.2  | Pixel V2                                                                                  | 105 |  |

|          | 5.2             | Design | n of AROM-1                                                                               | 108 |  |

|          |                 | 5.2.1  | AROM-1 A/B/C                                                                              | 109 |  |

|          |                 | 5.2.2  | AROM-1 E/F                                                                                | 111 |  |

|          | 5.3             | Labor  | atory measurement                                                                         | 115 |  |

|          |                 | 5.3.1  | Experimental setup                                                                        | 115 |  |

|          |                 | 5.3.2  | Measurements with an ${}^{55}$ Fe iron source $\ldots \ldots \ldots \ldots \ldots \ldots$ | 116 |  |

|          |                 | 5.3.3  | Characterization of the full in-pixel circuitry                                           | 118 |  |

|          |                 | 5.3.4  | Characterization of the in-pixel discriminator                                            | 122 |  |

|          | 5.4             | Summ   | ary                                                                                       | 124 |  |

| 6        | Sun             | nmary  | and conclusions                                                                           | 127 |  |

|          | 6.1             | Work   | summary                                                                                   | 128 |  |

|          | 6.2             | Gener  | al conclusions and discussions                                                            | 130 |  |

|          |                 | 6.2.1  | The MISTRAL/ASTRAL development                                                            | 131 |  |

|          |                 | 6.2.2  | The ALPIDE development                                                                    | 134 |  |

|          |                 | 6.2.3  | Some perspectives for CPS                                                                 | 135 |  |

| A        | Noi             | se sum | nmary of the AROM prototypes                                                              | 137 |  |

| Bi       | ibliography 139 |        |                                                                                           |     |  |

# List of Figures

| 1   | Digramme fonctionnel du capteur MIMOSA 28                                                                                                                                                                                                                                 | xvi   |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 2   | Schéma physique du capteur AROM-0                                                                                                                                                                                                                                         | xviii |

| 3   | Schéma physique du capteur AROM-1                                                                                                                                                                                                                                         | xix   |

| 4   | Schéma physique du capteur FSBB-A0                                                                                                                                                                                                                                        | xxi   |

| 5   | Digramme fonctionnel du capteur ASTRAL                                                                                                                                                                                                                                    | xxi   |

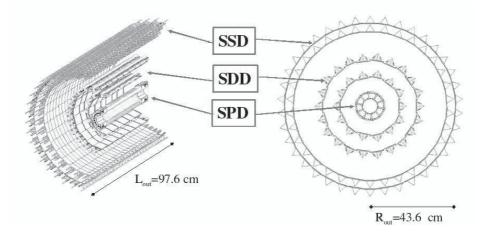

| 1.1 | The layout of the current ALICE ITS                                                                                                                                                                                                                                       | 3     |

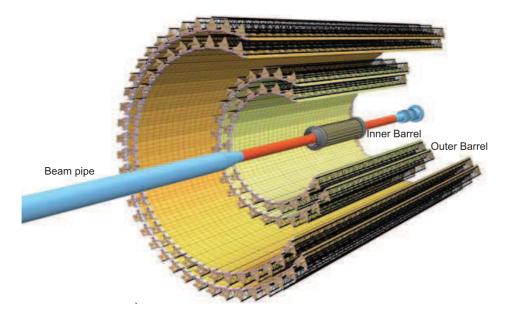

| 1.2 | The layout of the new ALICE ITS                                                                                                                                                                                                                                           | 9     |

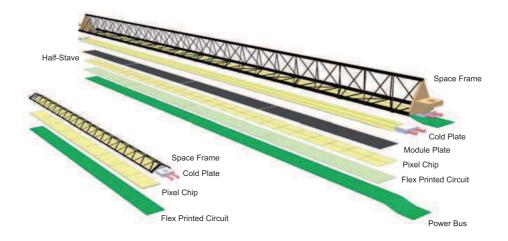

| 1.3 | Schematically drawing of the Inner Barrel (left) and the Outer Barrel (right) Staves                                                                                                                                                                                      | 10    |

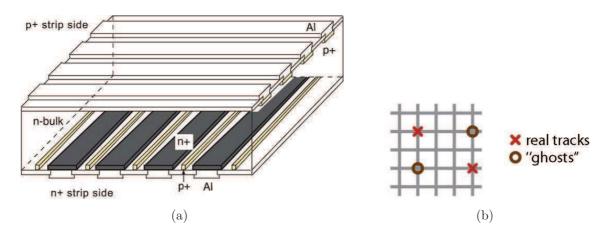

| 1.4 | (a) The double-sided strip detector. (b) True hits and ghost hits in double-sided strip detectors in case of two particles traversing the detector.                                                                                                                       | 12    |

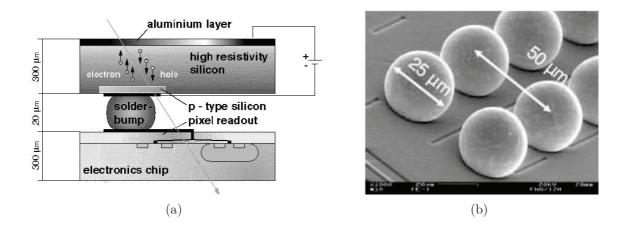

| 1.5 | (a) Cross-section view of a hybrid pixel detector and (b) an array of solder bumps.                                                                                                                                                                                       | 13    |

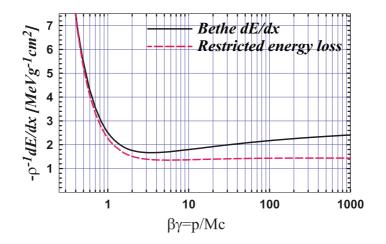

| 2.1 | The mean rate of energy loss for pions in silicon as a function of the ratio between the particle momentum $p$ and the particle mass $M$                                                                                                                                  | 20    |

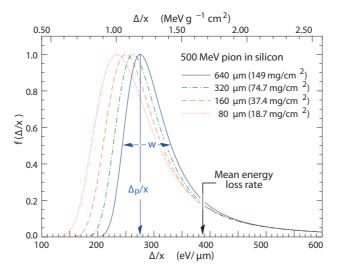

| 2.2 | Straggling functions $f(\Delta/x)$ in silicon for 500 MeV pions, normalized<br>to unity at the most probable value. $x$ is the silicon thickness; $\Delta$ is the<br>energy loss; $\Delta_p/x$ is the most probable energy loss; $w$ is the full width<br>at half maximum | 21    |

|     |                                                                                                                                                                                                                                                                           |       |

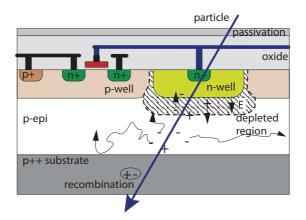

| 2.3 | The cross section view of a single cell of a CMOS pixel sensor. The<br>epitaxial layer, commonly used in modern CMOS processes, forms the<br>active volume of the detector. Typically, the thickness of the epitaxial                                                                                                                                 |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | layer is limited to approximately 15 $\mu$ m. The charge collection diode is<br>formed by the implanted N-well reaching the epitaxial layer. The de-<br>pleted region appears in the vicinity of the diode. In the undepleted<br>region, the charge deposited in the active volume by an impinging ion-<br>izing particle moves by thermal diffusion. | 25 |

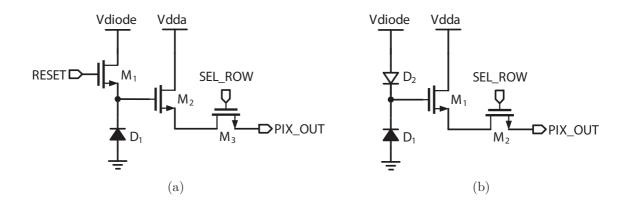

| 2.4 | (a) The 3T pixel and (b) the self-bias pixel.                                                                                                                                                                                                                                                                                                         | 25 |

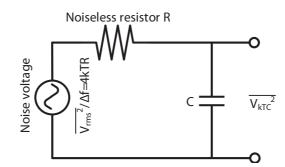

| 2.5 | Noise in a RC circuit.                                                                                                                                                                                                                                                                                                                                | 34 |

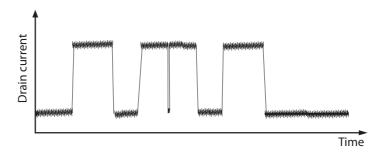

| 2.6 | The drain current as a function of time for a transistor exhibiting RTS.                                                                                                                                                                                                                                                                              | 35 |

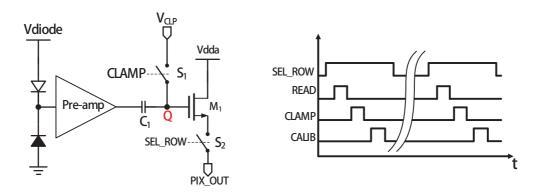

| 2.7 | A typical CMOS pixel with in-pixel CDS (left) and the corresponding chronogram for operation (right).                                                                                                                                                                                                                                                 | 37 |

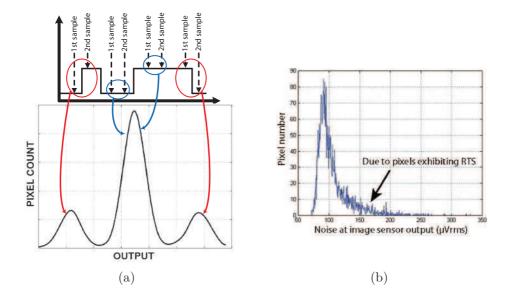

| 2.8 | (a) Illustration of three output states of a pixel, resulting from the two<br>level RTS noise, and (b) the noise distribution of all the pixels in a                                                                                                                                                                                                  | 20 |

|     | CMOS image sensor.                                                                                                                                                                                                                                                                                                                                    | 38 |

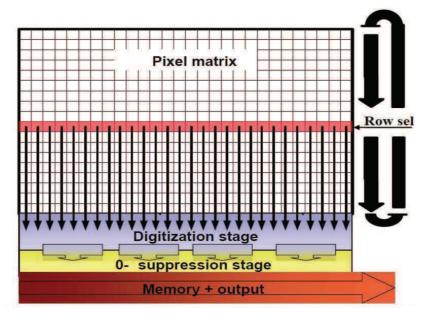

| 2.9 | The global architecture of a rolling shutter CPS                                                                                                                                                                                                                                                                                                      | 40 |

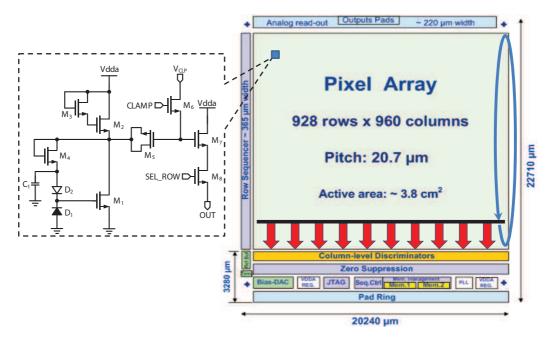

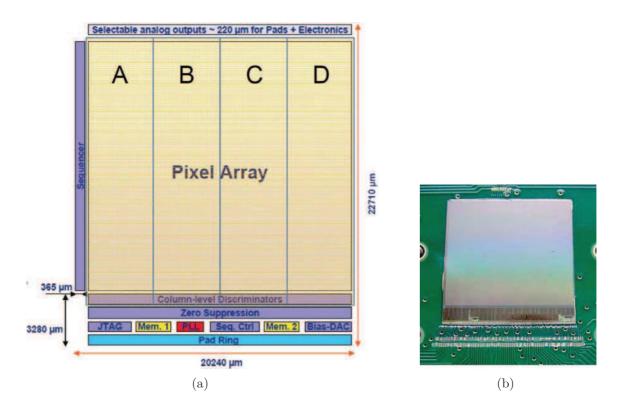

| 3.1 | (a) Functional block diagram of the ULTIMATE sensor and (b) The picture of the sensor on its PCB.                                                                                                                                                                                                                                                     | 44 |

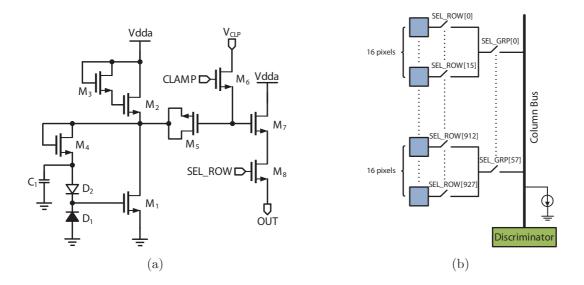

| 3.2 | (a) Schematic of one pixel. (b) Each 16 pixels in a column are grouped together and selected by the SEL_GRP signal in order to reduce the pagesitie expectations seen by the output pade                                                                                                                                                              | 16 |

|     | parasitic capacitance seen by the output node.                                                                                                                                                                                                                                                                                                        | 46 |

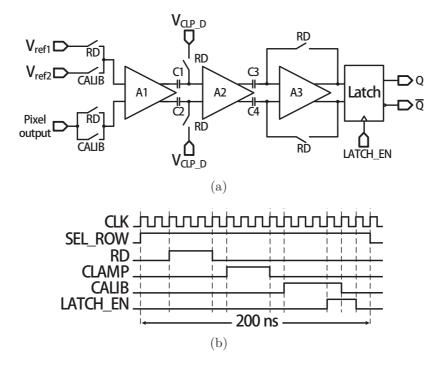

| 3.3 | (a) Schematic of the discriminator. (b) The timing diagram                                                                                                                                                                                                                                                                                            | 47 |

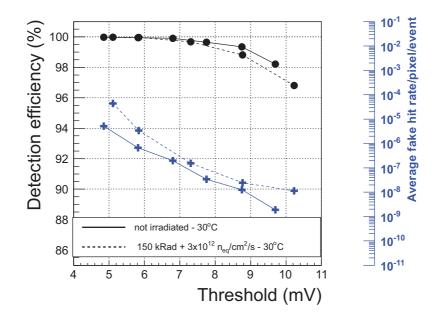

| 3.4 | Performances of the ULTIMATE sensor before and after irradiation doses corresponding to the STAR-PXL requirements.                                                                                                                                                                                                                                    | 49 |

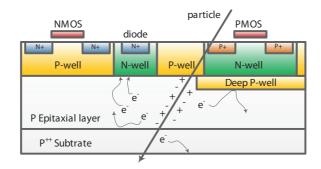

| 3.5 | Cross section view of a CMOS pixel cell with the deep P-well implant.<br>The deep P-well provides shielding to the N-well hosting the PMOS transistor.                                                                                                                                                                                                | 51 |

| 3.6 | Image of MIMOSA-32. The area framed by a dashed white line indicate the main block of interest, including 32 pixel sub-arrays.                                                                                                                                                                                                                        | 52 |

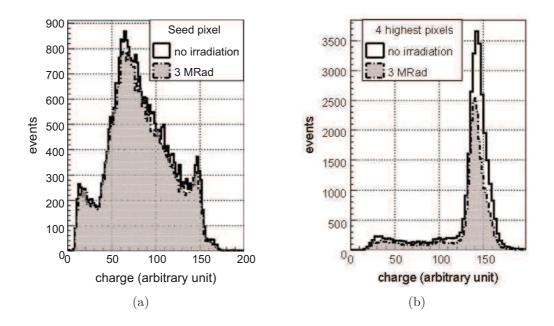

| 3.7  | The response to the $^{55}\mathrm{Fe}$ X-ray illumination of a sub-array in MIMOSA- |    |

|------|-------------------------------------------------------------------------------------|----|

|      | 32 before irradiation (solid empty histogram) and after a TID of 3 MRad             |    |

|      | (dotted filled histogram). (a) The charge collected by the seed pixel               |    |

|      | alone and (b) the charge collected by the set of 4 pixels in a cluster with         |    |

|      | the largest signal.                                                                 | 53 |

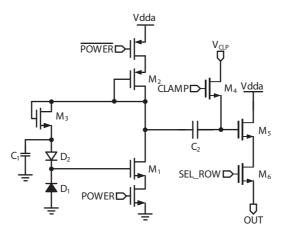

| 3.8  | The schematic of the pixel P25 in MIMOSA-32Ter                                      | 55 |

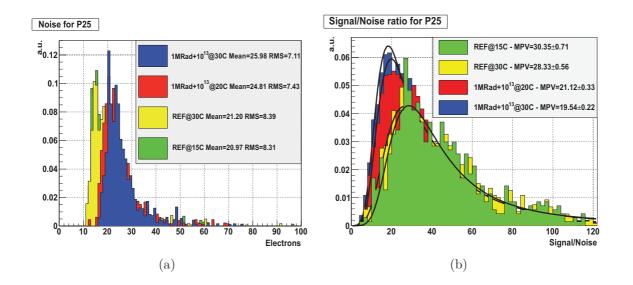

| 3.9  | (a) The noise distribution and (b) the SNR distribution for the cluster             |    |

|      | seed pixel of P25, before and after radiation doses of 1 MRad combined              |    |

|      | with $10^{13} n_{eq}/cm^2$ at two different coolant temperatures                    | 57 |

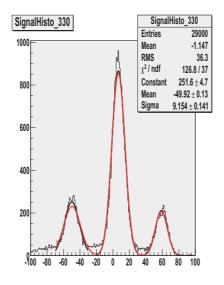

| 3.10 | The signal histogram of a single pixel in the P25 sub-array. The two                |    |

|      | peaks presented on both sides of the main peak indicate the existence               |    |

|      | of RTS noise.                                                                       | 58 |

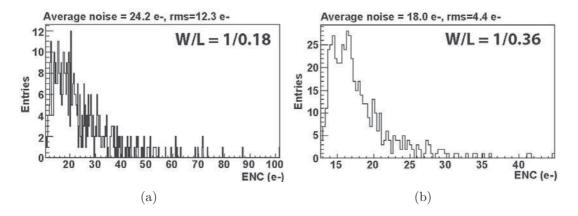

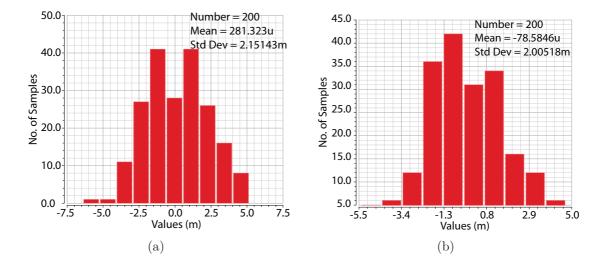

| 3.11 | Noise distributions for (a) the reference design in MIMOSA-32FEE1 and $\sim$        |    |

|      | (b) the pixel variant featuring a doubled length of the pre-amplifier's             |    |

|      | input transistor.                                                                   | 58 |

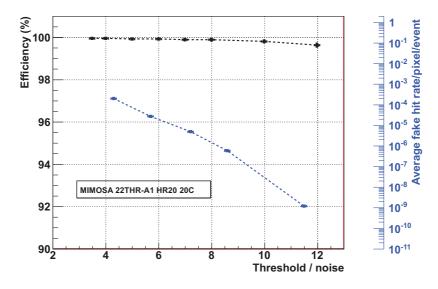

| 3.12 | The detection efficiency and fake hit rate measured with the electron               |    |

|      | beam at DESY, for the sub-array S2 in MIMOSA-22THR-A1                               | 59 |

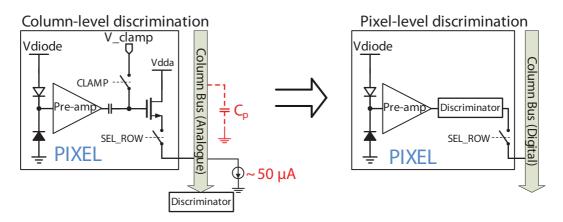

| 3.13 | Column-level discrimination vs. pixel-level discrimination.                         | 61 |

| 3.14 | The R&D roadmap towards the ASTRAL sensor dedicated to the ALICE-                   |    |

|      | ITS upgrade.                                                                        | 62 |

| 3.15 | The architecture of the proposed ASTRAL sensor for the ALICE-ITS                    |    |

|      | upgrade                                                                             | 62 |

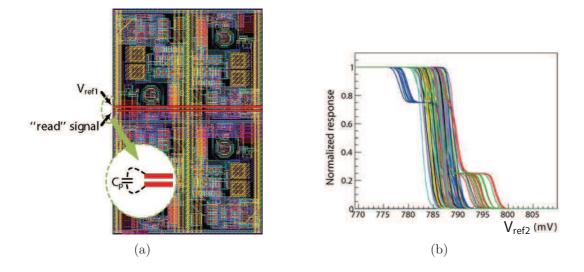

| 4.1  | The microscope image of AROM-0                                                      | 66 |

| 4.2  | The structure of a typical 32-row sub-array.                                        | 66 |

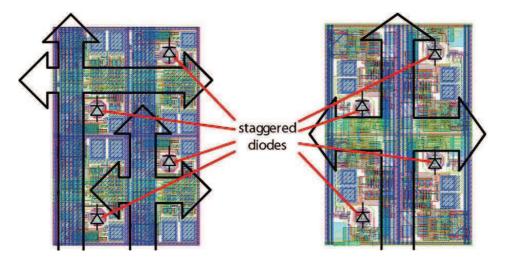

| 4.3  | Elongated pixels (a) without staggered diode placement and (b) with                 |    |

|      | staggered diode placement.                                                          | 67 |

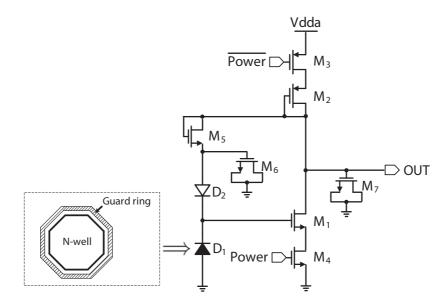

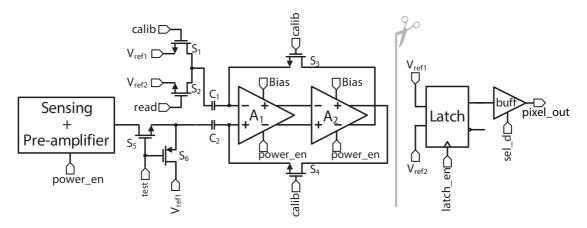

| 4.4  | Schematic of the sensing system in AROM-0                                           | 69 |

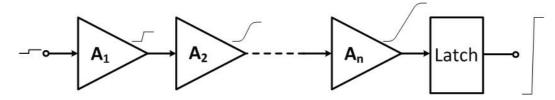

| 4.5  | Conceptual illustration of a comparator formed by a number of cascaded              |    |

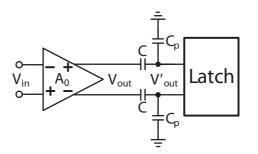

|      | amplifying stages and a latch.                                                      | 70 |

| 4.6  | The time constant ratio between the single stage approach and multiple              |    |

|      | stage approach, as a function of stage number. The total gain G is set              |    |

|      | to 50 (solid line) and 100 (dotted line), respectively                              | 72 |

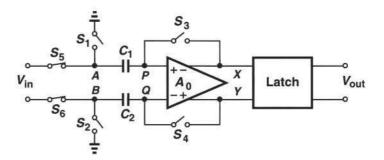

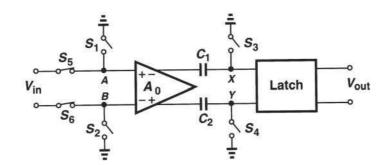

| 4.7  | The comparator employing IOS                                                        | 73 |

| 4.8  | The comparator employing OOS                                                        | 74 |

| 4.9  | The capacitive divider formed by the offset storage capacitor $C$ and the parasitic capacitor $C_p$ .                                                                                                                                                                                                                                    | 74 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.10 | Simplified schematic of pixel V1.                                                                                                                                                                                                                                                                                                        | 76 |

| 4.11 | Simplified schematic of pixel V2.                                                                                                                                                                                                                                                                                                        | 77 |

| 4.12 | Simplified schematic of pixel V3.                                                                                                                                                                                                                                                                                                        | 78 |

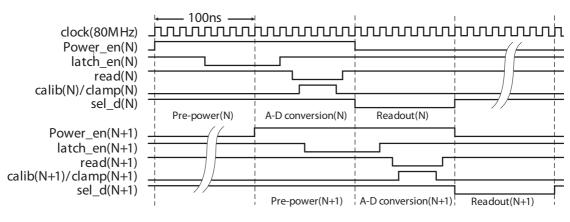

| 4.13 | Timing diagram.                                                                                                                                                                                                                                                                                                                          | 79 |

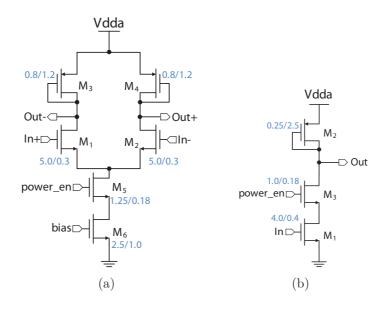

| 4.14 | The schematics of (a) the differential amplifier and (b) the single-ended amplifier used in AROM-0.                                                                                                                                                                                                                                      | 81 |

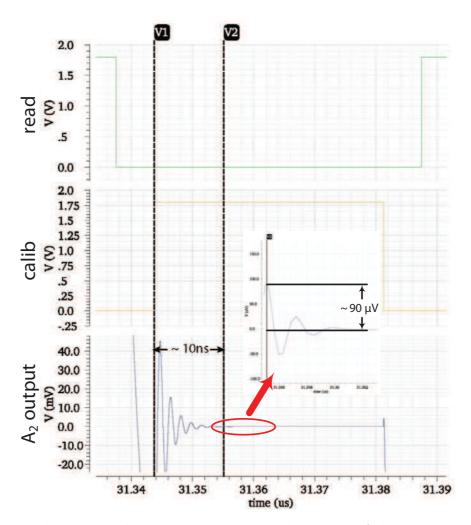

| 4.15 | The simulated transient response at the output of the second amplifier in V2.                                                                                                                                                                                                                                                            | 84 |

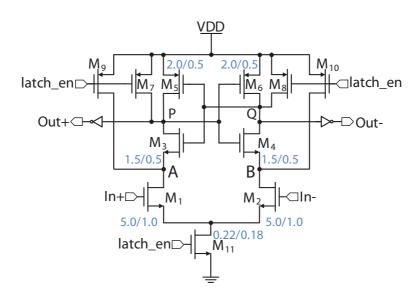

| 4.16 | Schematic of the dynamic latch                                                                                                                                                                                                                                                                                                           | 85 |

| 4.17 | Simulated offset distribution of the dynamic latch. (a) the mismatches of all the transistors are considered and (b) only the mismatch from the input pair is considered.                                                                                                                                                                | 87 |

| 4.18 | The layouts of the 4 pixels for V1 (left) and the double-row readout V2 (right). The black hollow arrows indicate the digital control signal distribution.                                                                                                                                                                               | 88 |

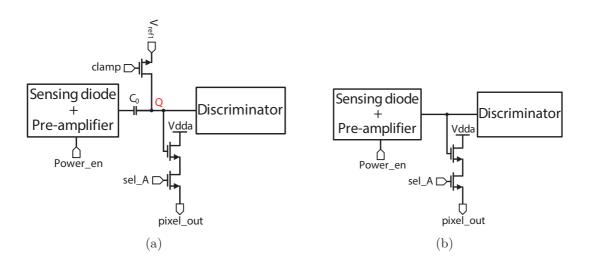

| 4.19 | Illustration of the analogue pixels for (a) pixel V1, and (b) pixel V2 (or V3)                                                                                                                                                                                                                                                           | 90 |

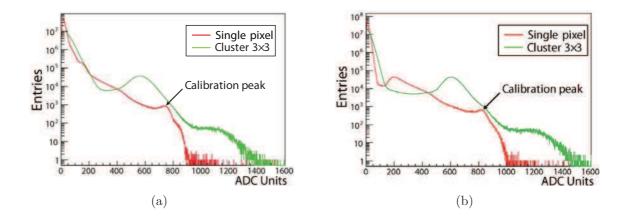

| 4.20 | Spectra of signals from an ${}^{55}$ Fe source, registered with (a) the four<br>analogue columns containing the pixel V1, and (b) the four analogue<br>columns containing the pixel V2. Both the signal distributions from<br>seed pixels (red) and the spectra of summed signals from $3 \times 3$ pixel<br>clusters (green) are shown. | 90 |

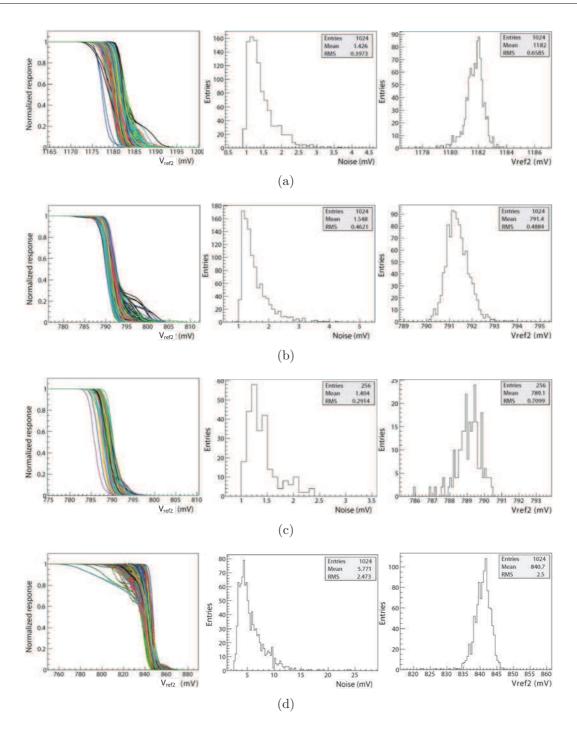

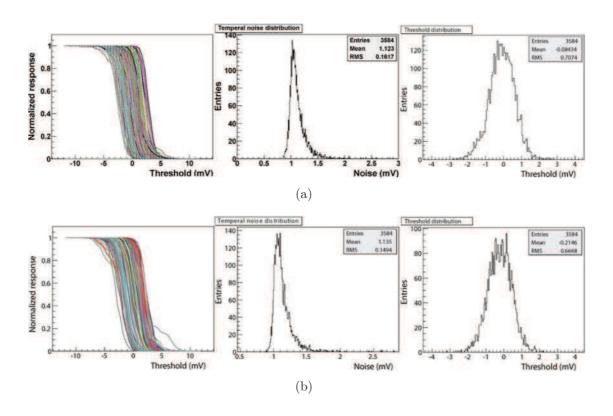

| 4.21 | "S" curves of the full in-pixel circuitry at the nominal speed (left), the extracted TN distributions (middle) and threshold distributions (right)                                                                                                                                                                                       |    |

|      | for (a) V1, (b) V2, (c) double-row readout V2 and (d) V3. $\ldots$                                                                                                                                                                                                                                                                       | 92 |

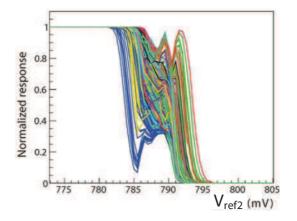

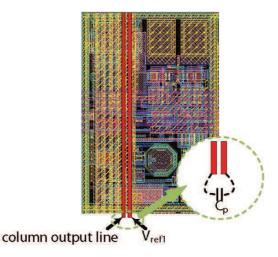

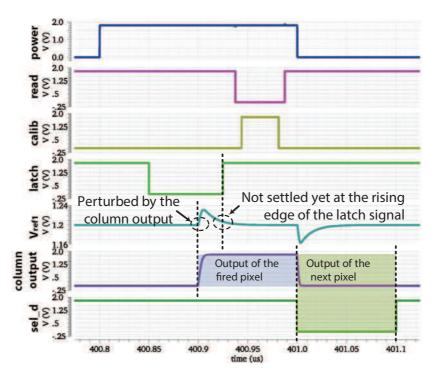

| 4.22 | The measured "S" curves for the in-pixel discriminator V2 at nominal speed. Due to the coupling between column data line and $V_{ref1}$ , the "S" curves are strongly disturbed.                                                                                                                                                         | 94 |

| 4.23 | The coupling between the digital output bus and the reference voltage                                                                                                                                                                                                                                                                    |    |

|      | $V_{ref1}$ .                                                                                                                                                                                                                                                                                                                             | 95 |

| 4.24 | The simulated wave forms including the parasitic parameters extracted<br>from layout. The voltage $V_{ref1}$ is disturbed by the activities on the<br>column output line.                                                                                                                     | 96  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.25 | (a) Illustration of the suspect coupling source (the layout shown con-<br>tains four pixels) and (b) the "S" curves of the in-pixel discriminators<br>measured at nominal speed for the double-row read-out V2                                                                                | 97  |

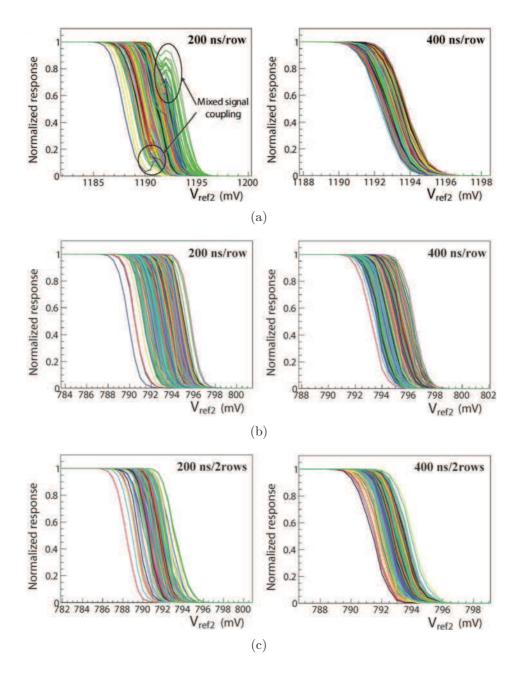

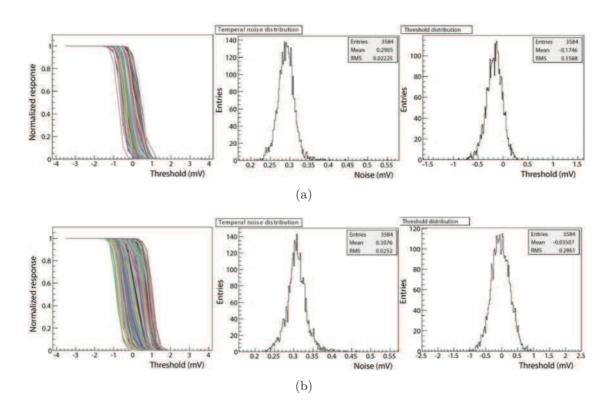

| 4.26 | "S" curves of the in-pixel discriminators when row processing time is 200 ns (left) and 400 ns (right): (a) V1, (b) V2 and (c) double-row readout V2.                                                                                                                                         | 98  |

| 4.27 | The illustration of the pixel used for latch measurement.                                                                                                                                                                                                                                     | 99  |

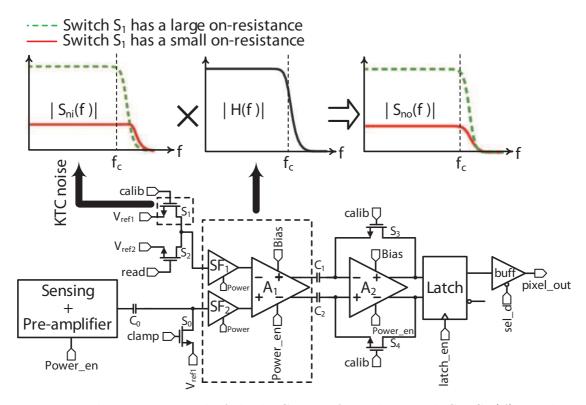

| 5.1  | The noise spectral of the kTC noise from the switch $S_1$ , $S_{ni}(f)$ , is shaped<br>by the transfer function $H(f)$ containing the source follower $SF_1$ and<br>the differential amplifier $A_1$ . $f_c$ is the cutoff frequency of $H(f)$                                                | 105 |

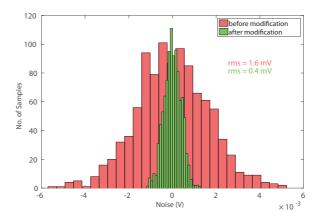

| 5.2  | The simulated noise distribution, referred to the discriminator input, before (green) and after (red) the modification for AROM-0 V1                                                                                                                                                          | 106 |

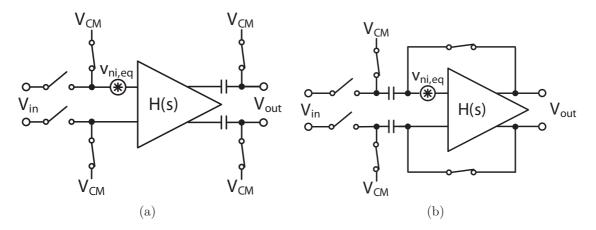

| 5.3  | Schematics of the circuits employing (a) OOS and (b) IOS during the auto-zeroing phase                                                                                                                                                                                                        | 106 |

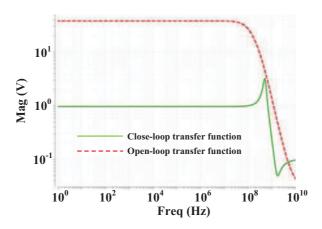

| 5.4  | The simulated close-loop (green solid line) and open-loop (red dashed line) transfer functions for the two-stage amplifier in AROM-0 V2                                                                                                                                                       | 108 |

| 5.5  | The layout of AROM-1.                                                                                                                                                                                                                                                                         | 108 |

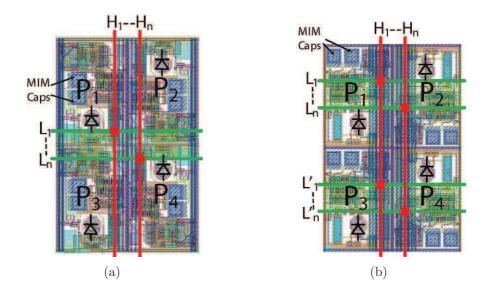

| 5.6  | The layout comparison of (a) AROM-1 A and (b) AROM-1 B. The<br>red lines represent the vertical metal lines (metal six) connecting the<br>sequence generator at the bottom of pixel matrix, and the green lines<br>represent the metal lines (metal five) distributing the control signals to |     |

|      | the corresponding row (or rows)                                                                                                                                                                                                                                                               | 110 |

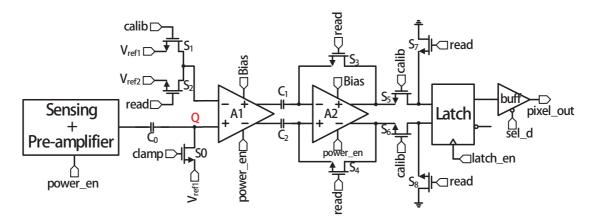

| 5.7  | The simplified pixel schematic for the AROM-1 E and AROM-1 F. $$ .                                                                                                                                                                                                                            | 111 |

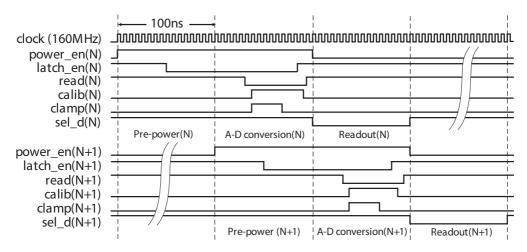

| 5.8  | The timing diagram of the AROM-1 E and AROM-1 F                                                                                                                                                                                                                                               | 112 |

| 5.9  | Simulated offset distribution of the dynamic latch used in AROM-1 $\mathrm{E/F}$                                                                                                                                                                                                              | 114 |

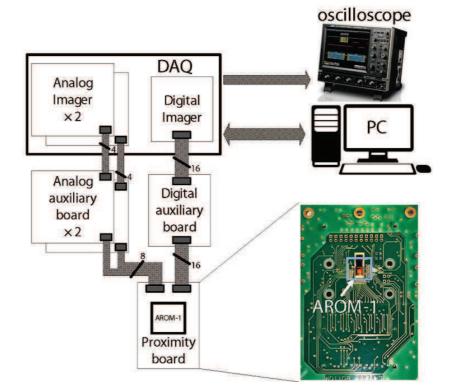

| 5.10 | The experimental setup for the test of AROM-1                                                                                                                                                                                                                                                 | 115 |

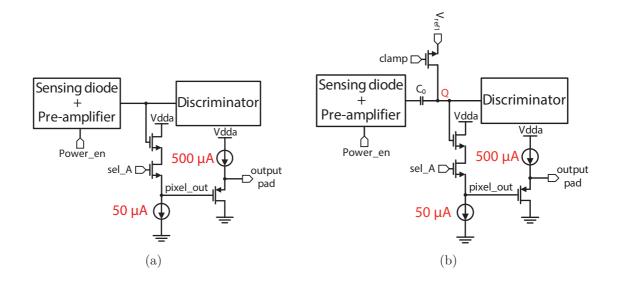

| 5.11 | The analogue output configuration for the AROM-1 pixels: (a) AROM-1 A/B/C, (b) AROM-1 E/F                                                                                                                                                                                                     | 117 |

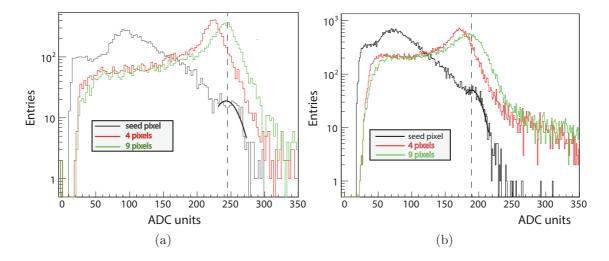

| 5.12 | The responses of the analogue pixels to the ${}^{55}$ Fe iron source for (a)               |     |

|------|--------------------------------------------------------------------------------------------|-----|

|      | AROM-1 B and (b) AROM-1 E. Black line: seed pixel. Red line: the                           |     |

|      | set of 4 pixels in a cluster with the largest signal. Green line: the set of               |     |

|      | 9 pixels in a cluster with the largest signal                                              | 117 |

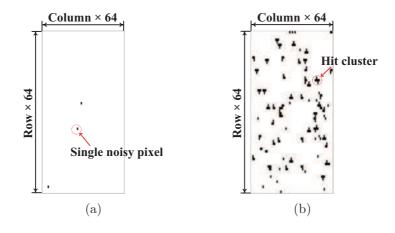

| 5.13 | Accumulated hit events after 70 read-out frames for an AROM-1 E chip                       |     |

|      | operating at 15 $^{\circ}\mathrm{C}$ with 100 MHz clock. (a) without the radiation source; |     |

|      | (b) with the radiation source.                                                             | 118 |

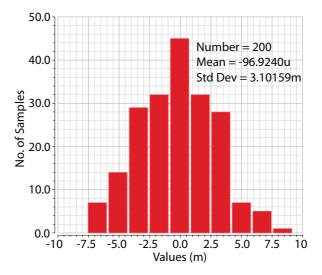

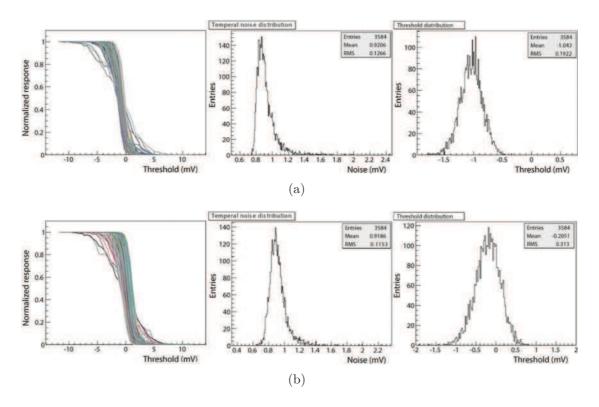

| 5.14 | "S" curves of the full in-pixel circuitry (left), the extracted TN distri-                 |     |

|      | butions (middle) and threshold distributions (right) for (a) AROM-1 B,                     |     |

|      | and (b) AROM-1 C. The readout speed is 160 ns/2-rows                                       | 120 |

| 5.15 | "S" curves of the full in-pixel circuitry (left), the extracted TN distri-                 |     |

|      | butions (middle) and threshold distributions (right) for (a) AROM-1 E,                     |     |

|      | and (b) AROM-1 F. The readout speed is 160 ns/2-rows                                       | 121 |

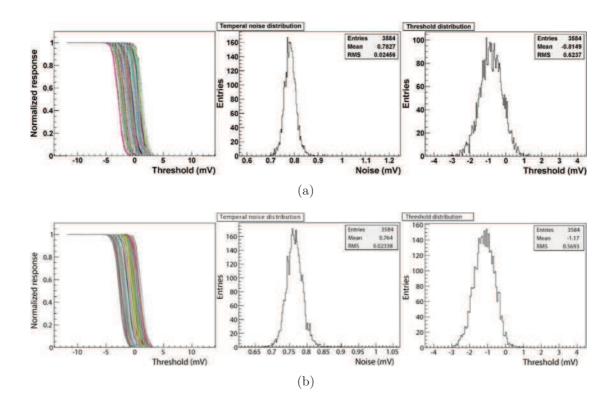

| 5.16 | "S" curves of the in-pixel discriminators, the extracted TN distributions                  |     |

|      | and threshold distributions for (a) AROM-1 B, and (b) AROM-1 C. The                        |     |

|      | readout speed is 160 ns/2-rows.                                                            | 123 |

| 5.17 | "S" curves of the in-pixel discriminators, the extracted TN distributions                  |     |

|      | and threshold distributions for (a) AROM-1 E, and (b) AROM-1 F. The                        |     |

|      | readout speed is 160 ns/2-rows.                                                            | 124 |

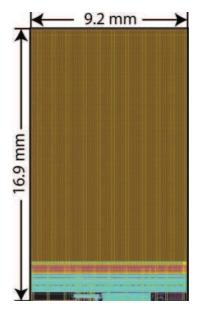

| 6.1  | The layout of the FSBB-A0.                                                                 | 129 |

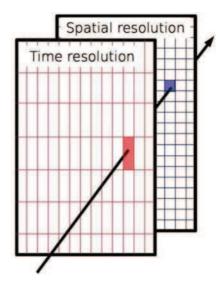

| 6.2  | Illustration of a double-sided detector, with one side providing high spa-                 |     |

|      | tial resolution and the other side providing time stamping                                 | 133 |

|      |                                                                                            |     |

# List of Tables

| 1.1 | Characteristics of the current ITS                                                                                                                                                                                                              | 4   |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.2 | Design parameters of the upgraded ITS                                                                                                                                                                                                           | 8   |

| 1.3 | General requirements on the pixel detector                                                                                                                                                                                                      | 10  |

| 3.1 | Comparison of the requirements of STAR-PXL and new ALICE-ITS, in<br>terms of read-out speed ( $\sigma_t$ ), intrisic spatial resolution ( $\sigma_{sp}$ ) and radia-<br>tion tolerance related to the total ionizing dose(TID) and non-ionizing |     |

|     | particle fluence.                                                                                                                                                                                                                               | 43  |

| 3.2 | Beam test results for selected pixel designs in MIMOSA-32                                                                                                                                                                                       | 54  |

| 3.3 | Beam test results for P25 in MIMOSA-32Ter                                                                                                                                                                                                       | 56  |

| 4.1 | Single point resolution corresponding to the binary cluster encoding for                                                                                                                                                                        |     |

|     | different pixel dimensions                                                                                                                                                                                                                      | 68  |

| 4.2 | Simulation results for the amplifiers used in AROM-0                                                                                                                                                                                            | 83  |

| 4.3 | Noise performance of the full in-pixel circuitry in AROM-0                                                                                                                                                                                      | 93  |

| 4.4 | Noise performance of the in-pixel discriminator in AROM-0. $\ldots$ .                                                                                                                                                                           | 99  |

| 4.5 | Noise performance of the latch.                                                                                                                                                                                                                 | 100 |

| 5.1 | Simulation results for the amplifiers used in AROM-1 E/F                                                                                                                                                                                        | 113 |

| 5.2 | Noise performance of the full in-pixel circuitry in AROM-1 A/B/C. $$ .                                                                                                                                                                          | 121 |

| 5.3 | Noise performance of full in-pixel circuitry in AROM-1 E/F                                                                                                                                                                                      | 122 |

| 5.4 | Noise performance of in-pixel discriminator in AROM-1 B/C. $\ . \ . \ .$                                                                                                                                                                        | 122 |

| 5.5 | Noise performance of in-pixel discriminator in AROM-1 E/F                                                                                                                                                                                       | 124 |

| 6.1 | Performances of the discriminators in different chips                                                                                                                                                                                           | 130 |

| A.1 | The AROM noise performance for the full in-pixel circuitry                                                                                                                                                                                      | 137 |

| A.2 | The AROM noise performance for the in-pixel discriminator                                                                                                                                                                                       | 138 |

## Acknowledgements

This thesis wouldn't be possible without the support and help of many individuals. Therefore, it is a great pleasure to express my gratitude to those who have helped, encouraged and accompanied me for the last four years.

To begin with, I would like to show my gratitude to my supervisor Prof. Yann HU, as well as to Dr. Christine HU-GUO, the director of the microelectronic team in IPHC (Institut Pluridisciplinaire Hubert Curien), and Dr. Marc WINTER, the leader of PICSEL group in IPHC, for offering me the opportunity to pursue my PhD research in France and providing me the guidance and invaluable suggestions throughout my PhD study.

I would also like to thank Prof. Marlon BARBERO, from CPPM (Centre de Physique des Particules de Marseille, Aix Marseille University), and Prof. Patrick GARDA, from University Pierre et Marie Curie (Paris VI), for their kindness to be the members of my defense jury as the reporters.

I am very grateful to all my colleges in IPHC: Claude COLLEDANI, Jerome BAU-DOT, Frederic MOREL, Abdelkader HIMMI, Gregory BERTOLONE, Isabelle VALIN, Mathieu GOFFE, Michal SZELEZNIAK, Maciej KACHEL, Gilles CLAUS, Mathieu SPECHT, Christian ILLINGER, Sylviane MOLINET and Guy DOZIERE for their kind help and technical support in my work. Especially, I would like to thank my colleges and dear friends, Andrei DOROKHOV and Pham Thanh Hung for sharing their vast knowledge with me and their enormous support on the chip measurements.

In addition, I am grateful for having so many colleges who share the same mother tongue. I'd like to thank Zhou Yang, Shi Zhan, Fang Xiaochao, Fu Yunan, Zhao Wei, Zhang Liang, Zhang Ying, Wang Jia and Liu Qingyuan for being friends with me and providing help not only in my work but also in my daily life.

Last but not the least, I would like to thank my parents who have shown so much understanding and been always there for me.

## Résumé en Français

La collaboration ALICE (A Large Ion Collider Experiment: expérience sur un grand collisionneur d'ions) prépare dès maintenant une importante amélioration des performances du détecteur ALICE. La mise à jour du détecteur est prévue pendant la longue période d'arrêt (LS2) de la machine LHC (Large Hadron Collider) en 2018/2019 visant à en augmenter la luminosité d'un facteur 10 par rapport à sa valeur noiminale. Le nouveau programme de physique de l'expérience ALICE impose la mise à jour du trajectometre interne (ITS: Inner Tracking System) qui va permettre de reconstruire les traces des particules chargées à faible impulsion et de déterminer leur point d'origine avec une plus grande précision. Le nouvel ITS va ainsi permettre d'améliorer d'un facteur 3 la résolution sur le point d'impact des particules par rapport à sa version actuelle. Il va devoir également traiter le flux de données très important produit par l'expérience. Face aux limitations des technologies existantes largement utilisées dans les différents trajectometres au LHC parmi lesquelles on peut citer les capteurs en silicium à micro-pistes ou à pixels hybrides, une nouvelle génération de capteurs plus fins et plus granulaires s'avère nécessaire pour réaliser ce défi technologique.

Les capteurs CMOS à pixels (CPS: CMOS Pixel Sensor ou MAPS), initiées par l'IPHC (Institut Pluridisciplinaire Hubert Curien, Strasbourg), sont d'excellent candidats pour ce domaine d'application car ils permettent de combiner granularité, faible épaisseur, tolérance aux radiations et vitesse de lecture. Plus de 30 prototypes de capteurs intitulés MIMOSA (Minimum Ionizing particle MOS Active pixel sensor) réalisés en technologie standard CMOS ont été développés depuis maintenant plus de 10 ans et leurs performances démontrées pour la réalisation de trajectometre de particules chargées. Ainsi, les capteurs ULTIMATE (alias MIMOSA 28), fabriqués en technologie CMOS 0.35  $\mu$ m, équipe depuis janvier 2014 le détecteur PXL (PIXEL) de l'expérience STAR (Solenoidal Tracker) au RHIC (Relativistic Heavy Ion Collider). Le pixel d'ULTIMATE comprend une diode de collection, un préamplificateur et un circuit CDS (Correlated Double Sampling: double échantillonnage corrélé). La matrice de pixels est lue ligne par ligne (en mode volet déroulant) pour réduire la consommation. Chaque colonne de pixels se termine par un discriminateur afin de convertir les signaux analogiques issus de la sortie des préamplificateurs en valeur binaire. Les résultats sont ensuite envoyés à la logique de suppression des zéros ("Zero suppression") permettant de réduire le flux de donnée à la sortie du capteur. Le schéma fonctionnel du capteur MIMOSA 28 et l'architecture du pixel sont illustrés par la Fig. 1

Figure 1: Digramme fonctionnel du capteur MIMOSA 28.

Le nouvel ITS de l'expérience ALICE partage, avec le PXL de l'expérience STAR, un but similaire qui est la reconstruction précise des particules à impulsion faible et de durée de vie courte. Cependant, par rapport au PXL, le nouvel ITS nécessite des améliorations substantielles des performances du capteur, en particulier la vitesse de lecture, la tolérance aux radiations et la puissance consommée.

L'équipe PICSEL (Physics with Integrated Cmos Sensors and ELectron machines) de l'IPHC s'est impliqué activement dans les développements de la nouvelle génération de CPS dédiée à la jouvence de l'ITS d'ALICE. Celle-ci s'appuie sur la technologie CIS (CMOS Image Sensor)  $0.18 \ \mu m$  fourni par *TowerJazz*. Les capteurs fabriqués dans cette nouvelle technologie ont montré une meilleure tolérance aux radiations que les capteurs ULTIMATE réalisé dans une technologie CMOS  $0.35 \ \mu m$  plus ancienne, satisfaisant déjà une des exigences de l'ITS. En outre, elle permet d'accroître considérablement la

capacité de traitement de signal dans le pixel. En effet, avec sa technologie à quatre puits (quadruple well), elle offre la possibilité d'implémenter des transistors de type P dans chaque pixel sans dégrader la capacité de collection de la diode. Il devient donc possible d'intégrer un discriminateur dans chaque pixel et obtenir un pixel à sortie binaire. Ce faisant, le traitement du signal analogique est contenu dans le pixel et le buffer analogique, qui charge la colonne de sortie sur une longue distance lorsque le discriminateur est en bas de la colonne, peut ainsi être retiré. En conséquence, la consommation de courant statique par pixel sera largement réduite. De plus, en ne devant considérer que les éléments parasites locaux de la chaîne de lecture analogique, le temps de traitement de la ligne peut être potentiellement réduit. À partir de cette étude, une nouvelle génération de prototypes de capteur CMOS à lecture rapide et à faible consommation dénommé AROM (Accelerated Read-Out MIMOSA: MIMOSA avec lecture accélérée) a été développée et est rapportée dans cette thèse. Basé sur ces nouveaux prototypes, le capteur ASTRAL (AROM Sensor for the inner TRacker of ALICE: capteur AROM pour le trajectometre interne d'ALICE) proposé pour la mise à jour de l'ITS d'ALICE devrait permettre de répondre à toutes les spécifications. Afin d'aboutir au capteur final, trois étapes de développement sont menés en parallèle. La première étape, à laquelle se rattache principalement ce travail, consiste à développer, valider et optimiser le concept du capteur CMOS avec l'intégration du discriminateur à l'intérieur du pixel. Différent versions de ce nouveau type de capteur AROM ont ainsi été réalisées. Les deux autres étapes de travail consistent à optimiser le système de détection (la diode de collection et le préamplificateur) et à étudier une logique de suppression des zéros adapté à l'environnement ALICE. Enfin, tous ces efforts se rejoindront pour concevoir le capteur final ASTRAL.

#### Les études réalisées dans cette thèse

L'objectif de cette thèse est de développer, à partir de plusieurs itérations de prototype du capteur AROM, un capteur qui serait l'élément de base du capteur final et dont les performances prometteuses, pourraient satisfaire pleinement les spécifications du nouvel ITS.

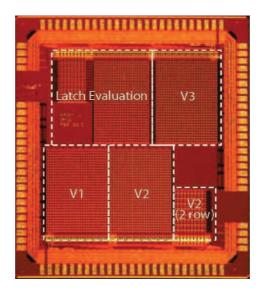

Dans la première partie de la thèse, un premier prototype de petite taille, intitulé AROM-0, a été conçu et fabriqué afin d'étudier la faisabilité de la discrimination de signal dans un petit pixel et d'évaluer ses performances. Dans ce prototype, chaque

Figure 2: Schéma physique du capteur AROM-0.

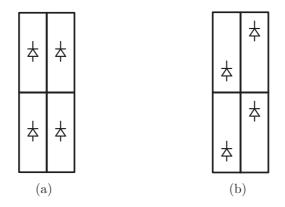

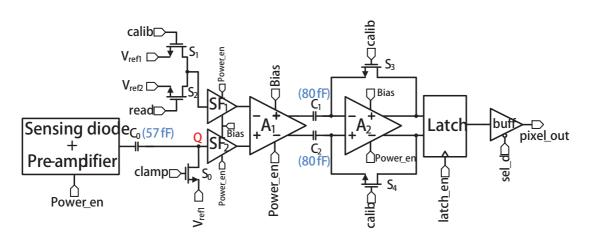

pixel de surface 22  $\mu$ m × 33  $\mu$ m contient une diode de détection, un préamplificateur et un discriminateur à tension d'offset compensée. Trois versions différentes de pixels, nommées V1, V2 et V3, ont été implémentées dans des matrices séparées contenant chacune 32 par 36 pixels. Les différences entre ces trois versions de pixels ne concernent que les topologies des discriminateurs. Par rapport au capteur ULTIMATE, le temps de lecture d'une ligne pour le capteur AROM est réduit de moitié passant de 200 ns/ligne à 100 ns/ligne. Sa consommation de courant statique par pixel est également divisée par au moins un facteur deux. Afin d'augmenter encore la vitesse de lecture, le pixel V2 a été implanté dans une matrice de 16 par 18 pixels qui est lue deux lignes par deux lignes. Les mesures en laboratoire ont montré que le bruit ENC (Equivalent Noise Charge) du circuit complet d'un pixel est d'environ 30 e<sup>-</sup> pour toutes les versions de pixels. Le discriminateur dans les pixels contribue autant au bruit total que le système de détection. Son bruit en tension est plus de 1 mV. Ce résultat est encourageants pour le premier prototype, mais la performance de bruit doit être améliorée. La distribution de bruit temporel (TN: temporal noise) présente une longue queue vers la valeur haute, ce qui est à cause du bruit télégraphique (RTS noise: Random Telegraph Signal noise) du préamplificateur. La contribution principale au bruit FPN (fixed pattern noise) du circuit complet est due au discriminateur. En raison de la complexité du layout, le bruit FPN pour la matrice avec une lecture par double ligne est plus grand que ce qui est avec une lecture par une seule ligne. La valeur de FPN dépend en grande partie des couplages capacitifs liée aux croisements des pistes dans le layout très dense du pixel. Des études postérieures ont mis en évidence une source de couplage critique entre un nœud sensible et un signal numérique qui aurait pu être évité par un dessin plus soigneux et par des simulations après routage. A partir des résultats de mesure, deux topologies de discriminateur ont été sélectionnés pour le développement suivant.

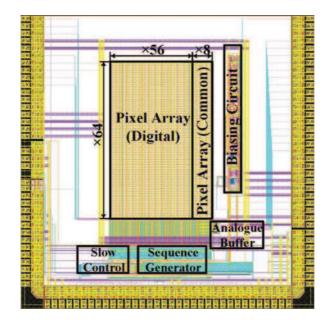

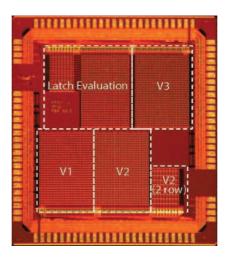

Figure 3: Schéma physique du capteur AROM-1.

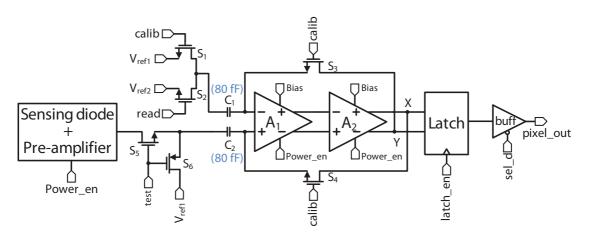

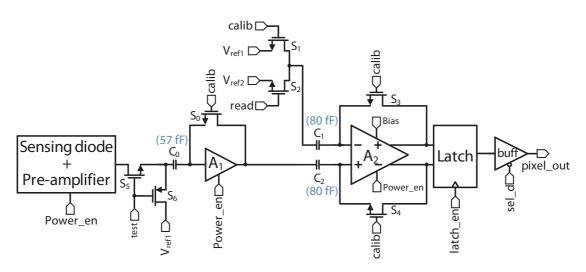

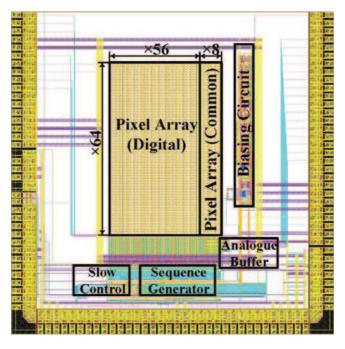

La deuxième partie de la thèse débute par l'analyse du bruit temporel des deux versions de pixel sélectionnées dans AROM-0. Cette étude a montré que le pixel V1 dans AROM-0 aurait un bon potentiel pour un fonctionnement à faible bruit à condition que de légères modifications soient apportées. Ensuite sera détaillé le développement des capteurs AROM-1. Ce sont les capteurs intermédiaires vers le capteur final ASTRAL. Ils ont deux objectifs principaux, l'un est de valider les optimisations de conception du pixel et l'autre est de mettre en place une architecture du capteur évolutive intégrant l'intelligence nécessaire dans le circuit. Comme l'illustre la Fig. 3, chaque AROM-1 contient une matrice de  $64 \times 64$  pixels qui est lue deux lignes par deux lignes. Les DACs (Digital to Analog Converter: Convertisseur numérique-analogique) de référence et le générateur de la séquence de lecture sont intégrés sur la périphérie du circuit; tous sont programmables à travers des registres JTAG (Joint Test Action Group) embarqués. La série de capteurs AROM-1 comporte cinq versions qui ont été réparties en deux groupes: le premier comprend les circuits AROM-1 A/B/C intégrant des pixels dérivés d'AROM-0 V2 ; le second comprend les circuits AROM-1 E/F incorporant des

pixels dérivés d'AROM-0 V1. Les variantes de pixel à l'intérieur d'un même groupe se différencient les unes des autres par le pas du pixel aussi bien que par le placement des composants et le routage des signaux dans le dessin du pixel. Tous les circuits ont été testés en laboratoire. L'utilisation d'une couche épitaxiée de haute résistivité dans AROM-1 a permis d'obtenir une plus grande efficacité de collection de charges. En outre, l'augmentation des dimensions des transistors d'entrée des préamplificateurs a contribué à la réduction du bruit RTS observé dans AROM-0. Le discriminateur implémenté dans AROM-1 E s'est montré le plus prometteur et a donc été choisi comme référence pour les développements à venir. Le circuit AROM-1 E est composé de pixels ayant le même pas que celui d'AROM-0. Le discriminateur, basé sur la topologie d'AROM-0 V1, a été optimisé afin de le rendre bas bruit et faible consommation. Le courant statique par pixel d'environ 18  $\mu$ A est beaucoup plus faible que celui consommé par le pixel d'AROM-0. Le bruit total du discriminateur d'AROM-E mesuré à 0.33 mV est significativement plus faible que celui de la génération précédente. Le bruit ENC de la chaîne complète du pixel, de l'ordre de 20 e<sup>-</sup>, est principalement dominé par la contribution du système de détection. S'appuyant sur le pixel d'AROM-1 E, AROM-1 F intègre une autre variante de discriminateur qui minimise la consommation en relaxant la contrainte sur les performances de bruit. Le pas du pixel d'AROM-1 F est de  $27 \ \mu m \times 27 \ \mu m$  pour lequel on s'attend à une résolution spatiale similaire au pixel de pas 22  $\mu$ m × 33  $\mu$ m. Le bruit du discriminateur d'AROM-1 F est mesuré à 0.42 mV avec un courant statique par pixel inférieure à 15  $\mu$ A.

#### Conclusions et perspectives

Le nouvel ITS de l'expérience ALICE sera équipée avec des capteurs CPS. Le capteur ASTRAL proposé par l'IPHC représente l'une des solutions pour cette application. Dans cette thèse, plusieurs variantes de capteurs incorporant la discrimination de signal à l'intérieur du pixel ont été développées dans une technologie CIS 0.18  $\mu$ m à quatre puits et sont les précurseurs d'ASTRAL. Les résultats de bruit très prometteurs du discriminateur dans le pixel combiné à une très faible consommation ont été démontrés dans les capteurs AROM. Par rapport à l'architecture de CPS classique comprenant une discrimination du signal en bas de la colonne, le capteur AROM ouvre des perspectives intéressantes en termes d'augmentation de la vitesse de lecture et de réduction de la consommation qui permettent d'approcher de très près les spécifications de l'ITS.

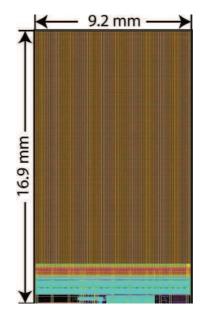

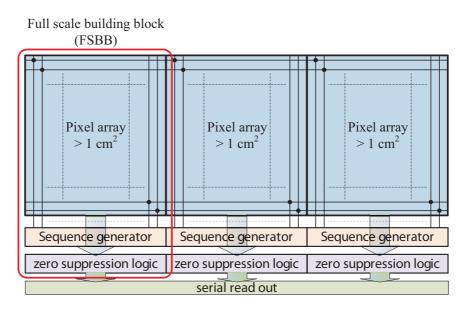

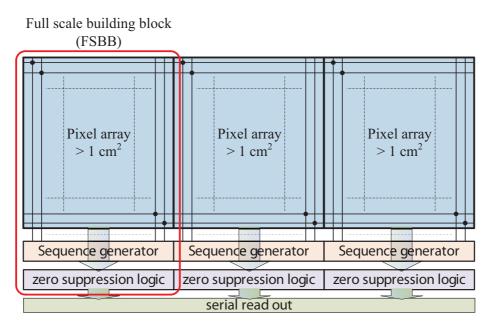

Figure 4: Schéma physique du capteur FSBB-A0.

L'élément de base pour le capteur ASTRAL, appelé FSBB-A (full scale building block for ASTRAL), a été construit en étendant l'architecture du capteur AROM-1 à une matrice de pixels pleine échelle occupant ainsi une surface sensible supérieure à 1 cm<sup>2</sup> et en intégrant la logique de suppression des zéros. Le capteur final ASTRAL sera composé de trois FSBB-A fonctionnant en parallèle et multiplexés au niveau de leurs noeuds de sortie. La Fig. 5 en donne un schéma fonctionnel du capteur ASTRAL.

Figure 5: Digramme fonctionnel du capteur ASTRAL.

Pour la suite de cette thèse, plusieurs questions concernant le capteur AROM doivent encore être résolus, notamment comprendre le faible rendement et l'absence des tensions de référence dans les capteurs AROM-1 et le capteur FSBB-A. En parallèle avec le développement d'ASTRAL, une autre architecture de CPS, également dédié au nouvel ITS, et comprenant un mode de lecture guidée par les données a été étudiée dans les prototypes ALPIDE (ALICE PIxel DEtector) conçus au CERN. Les capteurs ASTRAL et ALPIDE, tirant profit de l'évolution de la technologie CMOS, ont confirmé le potentiel des CPS qui ont été choisis pour la mise à jour de l'ITS d'ALICE ainsi que pour de nombreux autres projets à venir, comme par exemple le détecteur de vertex de l'ILC (International Linear Collider).

## Introduction

The ALICE collaboration is preparing for a major upgrade of its apparatus during the second long shut down of LHC (LS2) in the years 2018/2019. The proposed physics programs at ALICE require a new Inner Tracking System (ITS) with enhanced low-momentum vertexing and tracking capabilities, and at the same time allowing data taking at a substantially higher rate. Existing sensor technologies like microstrip detectors and hybrid pixels, which have been extensively employed in various experiments at LHC, are inadequate for this application. Therefore, a new generation of sensors, which would be much thinner and more granular than those in use, are required to equip the new ITS.

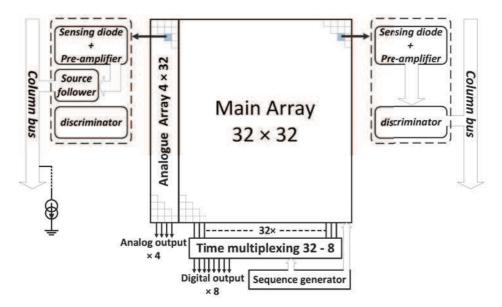

CMOS pixel sensors (CPS), pioneered at IPHC (Institut Pluridisciplinaire Hubert Curien, Strasbourg), are very attractive for this kind of applications, where the physics driven performances are privileged while relatively less stringent radiation tolerance and read-out speed are required. During the last fifteen years, more than 30 different MIMOSA (Minimum Ionizing particle MOS Active pixel sensor) prototypes have been developed by using the standard CMOS processes, in order to demonstrate their capability for charged particle tracking and to optimize their performances. The UL-TIMATE sensor (alias MIMOSA 28), fabricated in a 0.35  $\mu$ m CMOS process, has been successfully used to equip the STAR (Solenoidal Tracker At RHIC) PIXEL detector (PXL). And it is the first vertex detector using CPS. The pixel of the ULTIMATE sensor contains a sensing diode, a pre-amplifier and a CDS element. The pixel array is read out row by row (the so called rolling-shutter read-out mode). Each pixel column is terminated by a discriminator to convert the analogue signals from the pixels into binary values. Then, these binary values are sent to a zero-suppression logic to reduce the data flow for serial output. The ALICE-ITS upgrade and the STAR-PXL detector are conceived with a similar purpose of accurately reconstructing the short lived and low momentum particles. This greatly encourages the use of CPS in the upgrade

ALICE-ITS. However, as compared to the STAR-PXL detector, the ALICE-ITS upgrade calls for some substantial improvements on the sensor performances, especially on read-out speed and radiation tolerance.

In order to break the limitations of the ULTIMATE sensor, a 0.18  $\mu$ m CMOS Image Sensor (CIS) process, provided by *TowerJazz*, was explored at IPHC. As compared to the 0.35  $\mu$ m process used for the ULTIMATE sensor, the CPS fabricated in the new process is more radiation tolerant, satisfying the requirement of the ALICE-ITS upgrade. In addition, the new process can greatly enhance the in-pixel signal processing capability, thanks to the innovative deep P-wells. Therefore, it is possible to place a discriminator inside each pixel, achieving a fully digital output pixel. By doing this, the strong analogue buffer, used in the conventional analogue pixel to drive the long distance column line, is removed. Thus, the power consumed for analogue readout and A-D conversion can be largely reduced. Moreover, by dealing with only the small local parasitics in the analogue readout chain, the row processing time can be potentially decreased.

In this thesis, the concept of in-pixel discrimination, was realized in the AROM (Accelerated Read-Out MIMOSA) prototypes by employing the 0.18  $\mu$ m process. After several iterations of prototyping the AROM sensors, a scalable CPS, with promising performances fully adapted to the ALICE-ITS upgrade, has been achieved. The thesis is organized as follows,

Chapter 1 introduces briefly the scientific motivation for the upgrade of the ALICE-ITS, addresses the limitations of the current ITS and gives an overview of the new ITS. Several silicon based detector technologies, that are currently mature enough for high energy physics experiments, are reviewed, among which the CMOS pixel sensor steps up as the most promising solution for this particular application.

Chapter 2 presents the basic physics principles of charge generation in materials after a passage of an ionizing particle, with an emphasis on silicon devices. The detection principle of the CMOS pixel sensor and its prominent features for charged particle detection are described. Then, the radiation induced effects, deteriorating the detector performance, are briefly reviewed. And the mechanisms of various internal electronic noise are presented. The chapter ends with the introduction of the global read-out architecture for a typical rolling shutter CMOS pixel sensor, which provides a great solution for high speed applications.

In Chapter 3, the state-of-the-art CPS, called ULTIMATE, is first introduced as

the starting point for the ALICE pixel chip development. It is followed by a summary of some recent developments of the CPS based on a new 0.18  $\mu$ m quadruple-well CMOS process, directing the CPS to accommodate the requirements of the ALICE-ITS upgrade. Then, the roadmap towards the final sensor we have proposed for the ALICE-ITS upgrade, named ASTRAL (AROM Sensor for the inner TRacker of ALICE), is described.

The major part of this work follows the roadmap introduced in Chapter 3 and deals with the design of rolling shutter CMOS pixel sensors with in-pixel signal discrimination. As compared to the former CPS, with the signal discrimination performed at the column level, the sensors developed in this work can achieve a higher read-out speed, with a significantly reduced power consumption. Chapter 4 presents the design of the prototype chip named AROM-0, which contains several test structures to study the feasibility to realize the signal discrimination with a small pixel pitch, i.e.  $22 \times 33 \ \mu\text{m}^2$ . The measurement using a <sup>55</sup>Fe source and the noise evaluation using the "S" curve method are presented. Some improved pixel designs are integrated in a series of more advanced prototype chips named AROM-1. The AROM-1 sensor incorporates a larger pixel array and more periphery intelligence with respect to the AROM-0 prototype. Chapter 5 describes in detail the design and laboratory measurement results of those AROM-1 chips.

This work concludes in Chapter 6. The FSBB-A0 sensor, which is the first full-scale building block composing one third of the ASTRAL sensor, is introduced. Issues found in this work, which need to be addressed in the future, are discussed. Perspectives for using CPS in HEP (High Energy Physics), and their potential for applications beyond the HEP are presented.

# Chapter 1

# The ALICE-ITS upgrade

ALICE (A Large Ion Collider Experiment) [1] is a general-purpose, heavy-ion experiment at the CERN LHC (Large Hadron Collider)—the world's largest and most powerful particle accelerator. It is designed to study the physics of strongly interacting matter at extreme values of energy density and temperature in nucleus-nucleus collisions, where a phase of matter called quark-gluon plasma (QGP) forms.

Prior to the start-up of the LHC heavy-ion program, efforts were made at CERN SPS (Super Proton Synchrotron) and at BNL RHIC (Relativistic Heavy Ion Collider), revealing the nature of the QGP as almost "perfect" liquid [2–6]. ALICE has confirmed the RHIC observations and provided additional evidence of the existence of the QGP at the new energy regime [7], with the precision of measurements and kinematic reach exceeding those previously obtained for all significant probes of the QGP.

With the High Luminosity upgrade for the LHC (HL-LHC) after the second long shutdown (LS2) in 2018, it will be possible to achieve the luminosity to the order of at least  $L = 6 \times 10^{27} \text{ cm}^{-2} \text{s}^{-1} 1$ , with Pb beams reaching an interaction rate of about 50 kHz [8]. In order to fully exploit the scientific potential of the new LHC running conditions and to enhance the physics capabilities, the ALICE collaboration has devised a comprehensive upgrade strategy, enabling a detailed and quantitative characterization of the QGP with high statistics and high precision measurements [9–12].

The major goals of the proposed upgrade are:

• To increase the experiment's data-taking capabilities by at least an order of magnitude;

#### 1.1. THE PRESENT ALICE ITS AND ITS LIMITATIONS

- To extend the momentum reach at low transverse momenta (e.g., signals like low-mass di-leptons, );

- To open the possibility to study previously inaccessible rare probes (e.g.,  $\Lambda_c$  and  $\Lambda_b$ ).

Such a program relies on a new Inner Tracking System (ITS) with a significantly lower material budget and largely improved tracking and vertexing capabilities [13]. This is where the CMOS<sup>1</sup> pixel sensors fit in, and this thesis is devoted to the development of CMOS pixels sensors adapted to the new ALICE-ITS.

In this chapter, a brief introduction to the current ALICE-ITS and its limitations are first given. Then, the new requirements imposed on the upgraded ITS are outlined. After that, an overview of the expected new ITS, together with the general requirements on the sensor chip, is presented. Several silicon detector technologies, that are currently mature enough to be readily used in high energy particle experiments, are introduced. It can be seen that among the various detector technologies, CMOS pixel sensors will provide the most promising solution for the ALICE-ITS upgrade.

#### 1.1 The present ALICE ITS and its limitations

The ITS is a detector system installed at the heart of ALICE. Its main functions are

- reconstruction of the primary and secondary vertices;

- reconstruction of low- $p_T$  tracks that do not reach the ALICE Time Projection Chamber<sup>2</sup> (TPC);

- reconstruction of high- $p_T$  tracks that are lost inside the dead zones between the TPC sectors.

$<sup>^1{\</sup>rm CMOS}$  stands for Complementary Metal–Oxide–Semiconductor. It is a commonly used technology for constructing integrated circuits

<sup>&</sup>lt;sup>2</sup>The Time Projection Chamber (TPC) is the main tracking detector in the central barrel of the ALICE experiment at LHC. Its function is to provide track finding (efficiency larger than 90 %), charged particle momentum measurement (resolution better than 1 % for pions at about 1 GeV/c), particle identification (dE/dx resolution about 5.5 % in the non-relativistic region and statistically on the dE/dx relativistic rise up to  $p_T$  of a few tens of GeV/c), and two-track separation (resolution in relative momentum below 5 MeV/c) in the region  $p_T < 10$  GeV/c and pseudo-rapidity  $|\eta| < 0.9$ . [14]

It also aims to improve the momentum and angle resolution for particles reconstructed by the TPC. In addition, it contributes to the particle identification at low momenta (< 200 MeV/c) [15].

#### 1.1.1 Overview of the current ALICE ITS

Figure 1.1: The layout of the current ALICE ITS. (Source [15])

The current ALICE ITS, as shown in Fig. 1.1, consists of six cylindrical layers of silicon detectors coaxially surrounding the beam pipe, located at radii between 39 mm and 430 mm. They cover the pseudo-rapidity<sup>3</sup> range  $|\eta| < 0.9$  for vertices located within  $z = \pm 60$  mm with respect to the nominal interaction point. The innermost radius is the minimum allowed to approach the beam pipe, and the outermost one is determined by the track matching with the TPC. In order to achieve the required impact parameter<sup>4</sup> resolution and to cope with the high particle multiplicities expected in heavy-ion collisions at LHC (the system is designed for up to 100 particles per cm<sup>2</sup> for the inner layer [16]), the first two layers are composed of Silicon Pixel Detectors (SPD) using the hybrid detector technology. The two middle layers are made of Silicon Drift Detectors (SDD) which can provide truly two-dimensional information with only one dimensional readouts, however, at the expense of speed [17]. The two outer layers,

<sup>&</sup>lt;sup>3</sup>In experimental particle physics, pseudo-rapidity,  $\eta$ , is a commonly used kinematics variable describing the angle of a particle relative to the beam axis. It is defined as  $\eta \equiv -ln[tan(\frac{\theta}{2})]$ , where  $\theta$  is the angle between the particle three-momentum P and the positive direction of the beam axis.

<sup>&</sup>lt;sup>4</sup>The impact parameter of a track is defined as the distance of closest approach of the track to the interaction vertex. The two projections of the impact parameter, in the transverse plane and along the beam direction, are usually considered separately.

| Layer/Type | r (cm) | $\pm$ z (cm) | area $(m^2)$ | Intrinsic resolution<br>(r $\phi$ - z) ( $\mu$ m) | $\% X/X_0$ |

|------------|--------|--------------|--------------|---------------------------------------------------|------------|

| 1/Pixel    | 3.9    | 14.1         | 0.07         | 12 - 100                                          | 1.14       |

| 2/Pixel    | 7.6    | 14.1         | 0.14         | 12 - 100                                          | 1.14       |

| 3/Drift    | 15.0   | 22.2         | 0.42         | 35 - 25                                           | 1.13       |

| 4/Drift    | 23.9   | 29.7         | 0.89         | 35 - 25                                           | 1.26       |

| 5/Strip    | 38.0   | 43.1         | 2.20         | 20 - 830                                          | 0.83       |

| 6/Strip    | 43.0   | 48.9         | 2.80         | 20 - 830                                          | 0.83       |

Table 1.1: Characteristics of the current ITS.

where the track density decreases significantly compared to the inner layer (below one particle per cm<sup>2</sup>), are equipped with double-sided Silicon Strip Detectors (SSD). The four outer layers have analogue readout and therefore can be used for particle identification (PID) via dE/dx measurement in the non-relativistic  $(1/\beta^2)$  region. With careful optimization for each detector element, the ALICE ITS currently has the lowest material budget among various experiments at LHC, achieving between 0.8 % and 1.3 % of  $X_0^5$  per detector layer (in particular, 1.14 % of  $X_0$  for the SPD layer). Combining the thermal shields and supports inserted in between each group of two detector layers with the same technology, the total material budget for tracks perpendicular to the detector surface amounts to 7.63 % of  $X_0$ . Table 1.1 summaries the main characteristics of the current ITS [1, 18].

#### 1.1.2 The limitations of the current ALICE ITS

At mid-rapidity  $|\eta| < 0.9$ , the ITS is the key ALICE system for detecting particles containing heavy quarks. It is capable to precisely isolate the secondary decay vertices from the primary interaction vertex. The production of heavy flavour particles can therefore be studied by reconstructing their decays with a typical mean proper decay length ( $c\tau$ ) on the order of 100 - 300  $\mu$ m [19].

With the current ITS, the impact parameter resolution in the transverse plane  $(r\phi)$ at  $p_T > 1$  GeV/c is better than 75  $\mu$ m for pp collisions [20], and better than 65  $\mu$ m in the Pb-Pb case [21]. This precision is adequate to study the production of charm

<sup>&</sup>lt;sup>5</sup>Radiation length,  $X_0$ , is a characteristic of a material, related to the energy loss of high energy particles due to electromagnetic interactions with that material. It is defined as the mean distance over which a high-energy particle loses all but 1/e of its energy. Typically, the radiation length is multiplied by the material density, and so the  $X_0$  is measured in g·cm<sup>-2</sup>

mesons in exclusive decay channels (e.g.  $D^0 \to K\pi$  and  $D^+ \to K\pi\pi$ ) at transverse momentum values down to 2 GeV/c. However, at lower transverse momenta, the large combinatorial background leads to poor statistic significance of the measurement. The challenge is even greater for charm baryons, given that the most abundantly produced charm baryons ( $\Lambda_c$ ) have a mean proper decay length of only 60  $\mu$ m, which is lower than the impact parameter resolution of the present ITS in the transverse momentum range where the majority of  $\Lambda_c$  daughter particles is produced. For the same reasons, the study of beauty mesons, beauty baryons, and of hadrons with more than one heavy quark cannot be addressed by the current ITS [16].